Tool/software:

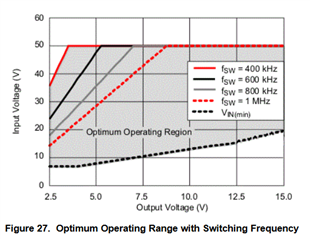

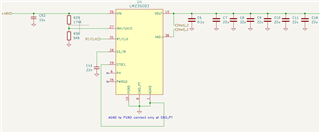

I am building a power supply board which will use the LMZ35033 to generate 5V, 12V from +48V. Any feedback is appreciated.

Design

- The only difference between the two configs is the Vset resistor (53.6K, 140K)

- and the RT clock resistor (1.1M, 267K) per the recommendations.

- Divider for UVLO chosen for '40.0V (~83% of nominal input)

Questions/comments

1) I do not need PWRGD functionality. Can i leave it floating, or should I ground it? The datasheet says "a pull up resistor is required" but perhaps it is only means "is required if you want to use it"

2) I have a TVS on the input (not shown, SMAJ48A-13-F) to protect against transients on startup. Is this a good choice, or is there something better?

3) Output capacitance: I have 6x 22 uF (132 uF). These (C3225X7R1C226M250AC) retain 84 uF even at 12V bias. The ones in the EVM do not obey the guidelines in the datasheet. First, in that its only 88 uF at 0V bias, and also by 12V bias the output capacitance drops to 26 uF.