Other Parts Discussed in Thread: TIDA-00653,

Tool/software:

Dear TI Experts,

Reference project: TIDA-00653、UCD3138FW-BIDI

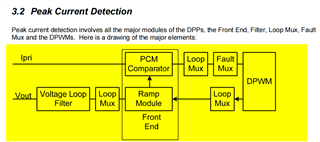

We plan to use the TIDA-00653 as a reference circuit and add PCM functionality. However, I found that PCM is controlled by the EADC, and since the TIDA-00653 circuit has four-phase current, it seems that using EADC's PCM for each phase is not feasible.

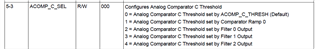

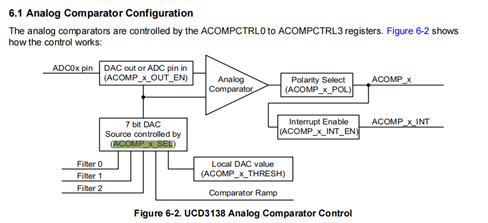

Currently, we are focusing on CBC. I found that the comparator source for CBC can select a filter as the source. If "ACOMP_x_SEL" selects the filter as the source, does the filter need any specific configuration? Where can we view the corresponding values for the filter source?

Alternatively, do you have other recommendations for PCM control that could be applied to four-phase current?

To simply test and verify the configuration EADC0 -> Filter0 -> CBC -> DPWM1, how should I set it up?

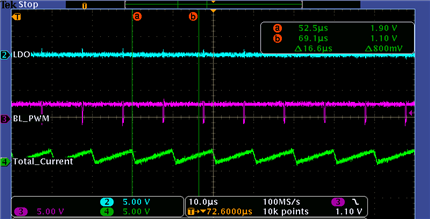

Below is my configuration. Is there any issue with these settings? After I completed the setup and enabled the CBC function, DPWMA remains in a fully LOW state. Neither controlling EADC’s EAP0 nor adjusting the DAC_Value produces any change.

void eadc_filter_cbc()

{

/* dpwm 1 */

Dpwm1Regs.DPWMCTRL0.bit.PWM_EN = 0; //disable locally for init

Dpwm1Regs.DPWMCTRL0.bit.CLA_EN = 0; //default is 1 - use cla

Dpwm1Regs.DPWMCTRL0.bit.PWM_MODE = 0; //normal mode

Dpwm1Regs.DPWMPRD.all = DPWM_PERIOD; //use .all for all values, make sure scaling matches.

Dpwm1Regs.DPWMEV1.all = (DEAD_TIME_1) + 10; //Put event 1 at start of period

Dpwm1Regs.DPWMEV2.all = ((DPWM_PERIOD) >> 1) - (DEAD_TIME_2) / 2; //1/4 of period - divide is OK because it's all constants.

Dpwm1Regs.DPWMEV3.all = ((DPWM_PERIOD) >> 1) + (DEAD_TIME_2) / 2; //1/2 of period

Dpwm1Regs.DPWMEV4.all = 10;

Dpwm1Regs.DPWMSAMPTRIG1.all = 2000;

Dpwm1Regs.DPWMMINDUTYHI.all = 2250;

Dpwm1Regs.DPWMMINDUTYLO.all = 2250;

Dpwm1Regs.DPWMCTRL0.bit.MIN_DUTY_MODE = 2;

Dpwm1Regs.DPWMCTRL0.bit.PWM_EN = 1; //enable locally

/* filter 0 */

Filter0Regs.FILTERKPCOEF0.bit.KP_COEF_0 = 1;

Filter0Regs.FILTERKICOEF0.bit.KI_COEF_0 = 0;

Filter0Regs.FILTERKDCOEF0.bit.KD_COEF_0 = 0;

Filter0Regs.FILTERKDALPHA.bit.KD_ALPHA_0 = 0;

Filter0Regs.FILTERKICLPHI.bit.KI_CLAMP_HIGH = 0x7FFFFF;

Filter0Regs.FILTERKICLPLO.bit.KI_CLAMP_LOW = 0;

Filter0Regs.FILTEROCLPHI.bit.OUTPUT_CLAMP_HIGH = 0x7FFFFF;

Filter0Regs.FILTEROCLPLO.bit.OUTPUT_CLAMP_LOW = 0;

Filter0Regs.FILTERCTRL.bit.FILTER_EN = 1;

// enable OK here, because nothing will happen until DPWM and front end are globally enabled

// Better option for handling shoot through - uses full dynamic range of filter

Filter0Regs.FILTERCTRL.bit.OUTPUT_MULT_SEL = 1; // select half period kcomp for output multiplier

/* loop mux */

// LoopMuxRegs.DPWMMUX.bit.DPWM0_FILTER_SEL = 0; // use filter 0 for DPWM 1

LoopMuxRegs.SAMPTRIGCTRL.bit.FE0_TRIG_DPWM1_EN = 1; // use DPWM1 for filter0 sample trigger

LoopMuxRegs.FILTERMUX.bit.FILTER0_FE_SEL = 0; // connect filter 0 to front end 0.

LoopMuxRegs.FILTERMUX.bit.FILTER0_PER_SEL = 1; // Selects source of switching cycle period for Filter 0 Module

/* eadc */

FeCtrl0Regs.EADCDAC.bit.DAC_VALUE = 8192;

FeCtrl0Regs.EADCCTRL.bit.AFE_GAIN = 2;

/* global */

union GLBEN_REG glben_store; // collect global enable bits for simultaneous use

glben_store.all = 0;

glben_store.bit.DPWM1_EN = 1;

glben_store.bit.FE_CTRL0_EN = 1;

LoopMuxRegs.GLBEN = glben_store;

/* cbc - dpwm1 */

//Phase 1 CBC

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_B_SEL = 2; // 2 = Analog Comparator B Threshold set by Filter 0 Output

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_B_POL = 1; // 1 = Comparator result enabled when input exceeds threshold (Default)

FaultMuxRegs.ACOMPCTRL0.bit.ACOMP_EN = 1; //1 = Analog Comparators Enabled

FaultMuxRegs.DPWM1CLIM.bit.ACOMP_B_EN = 1; //AD03 //1 = Analog Comparator result enabled for current limit

Dpwm1Regs.DPWMCTRL0.bit.CBC_ADV_CNT_EN = 1; //1 = CBC enabled (pwm mode: normal mode)

Dpwm1Regs.DPWMCTRL0.bit.CBC_PWM_AB_EN = 1; //1 = PWM-A and PWM-B affected by Fault CBC

}