Other Parts Discussed in Thread: UCC28951

Tool/software:

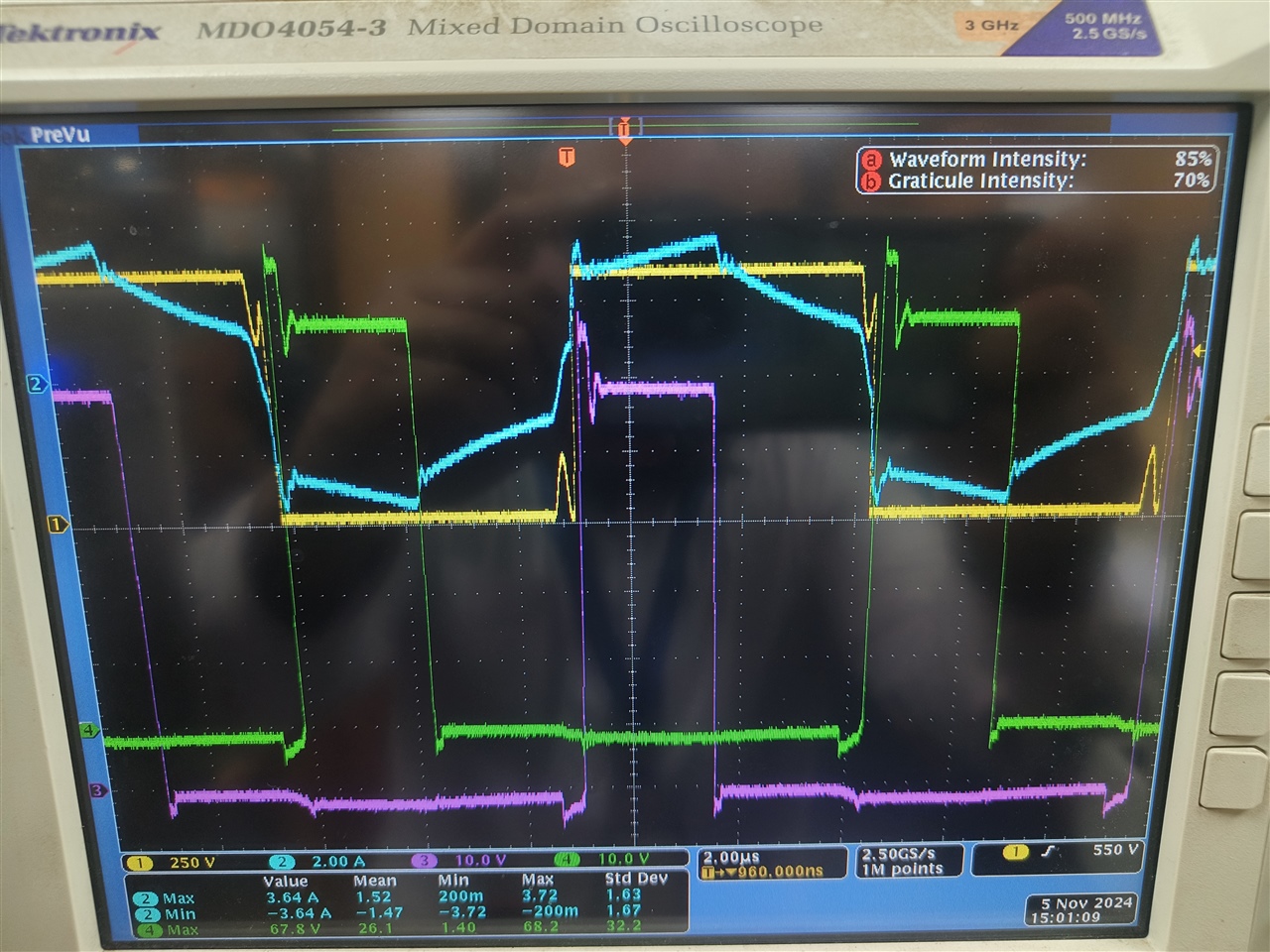

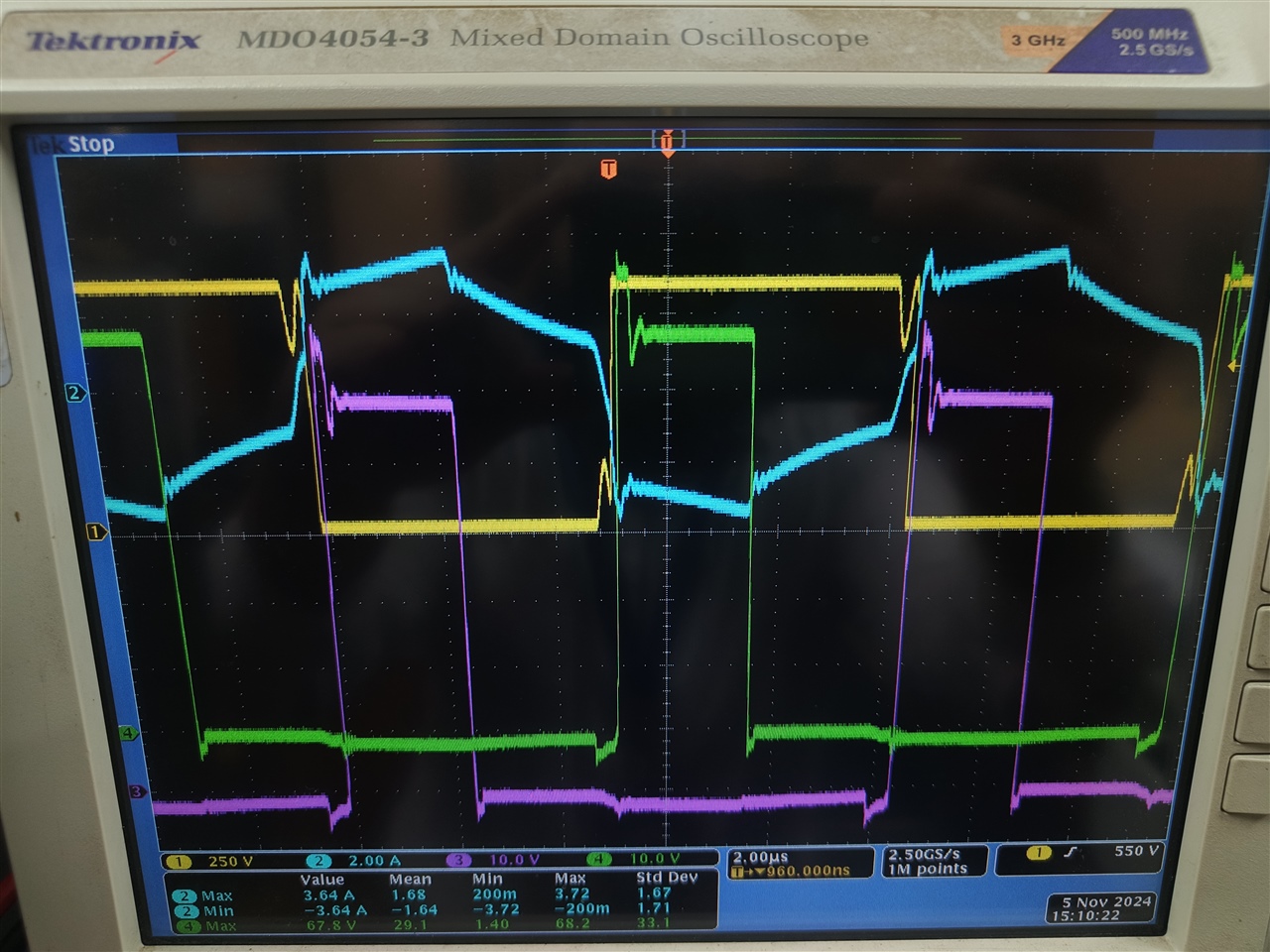

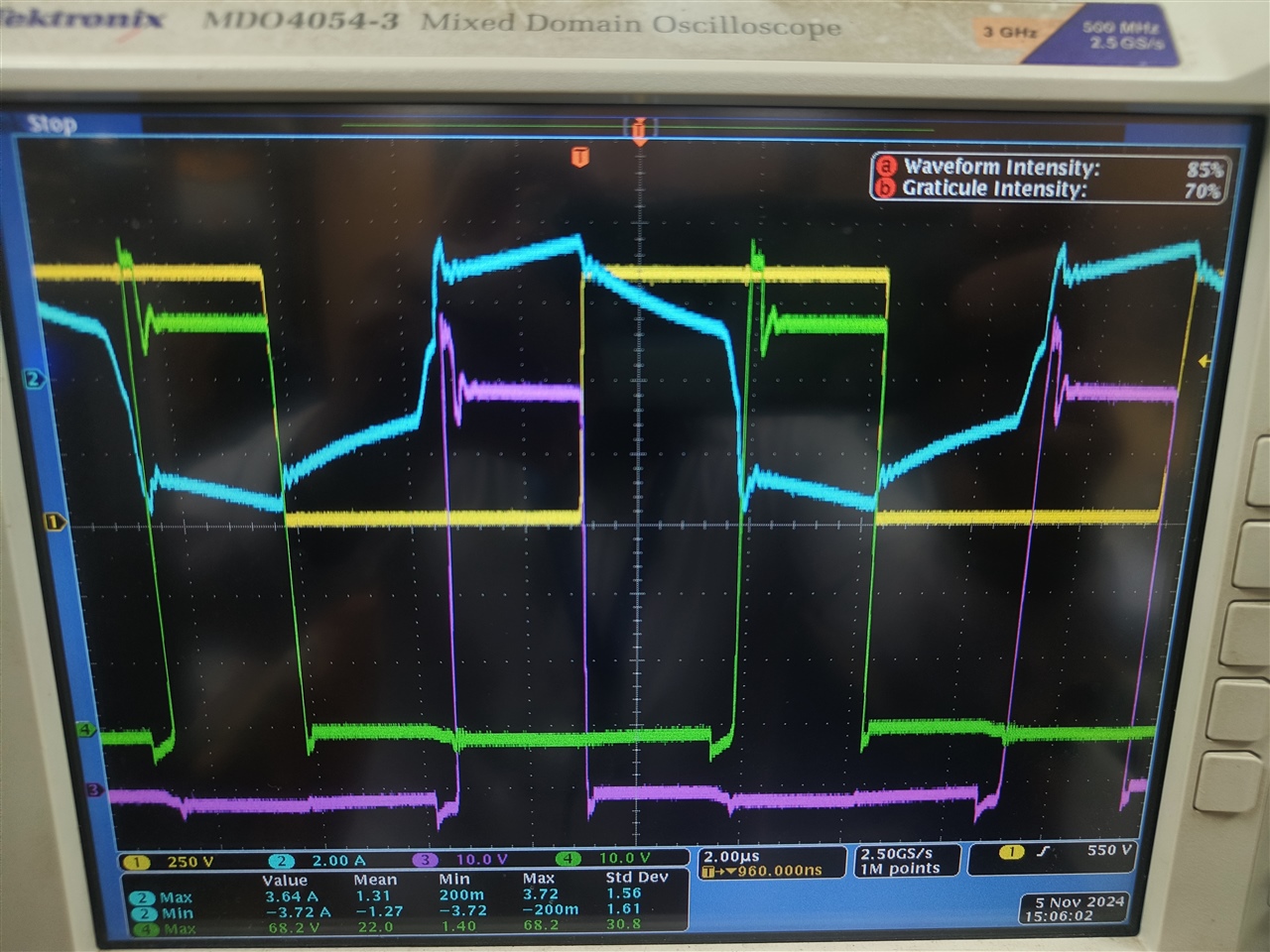

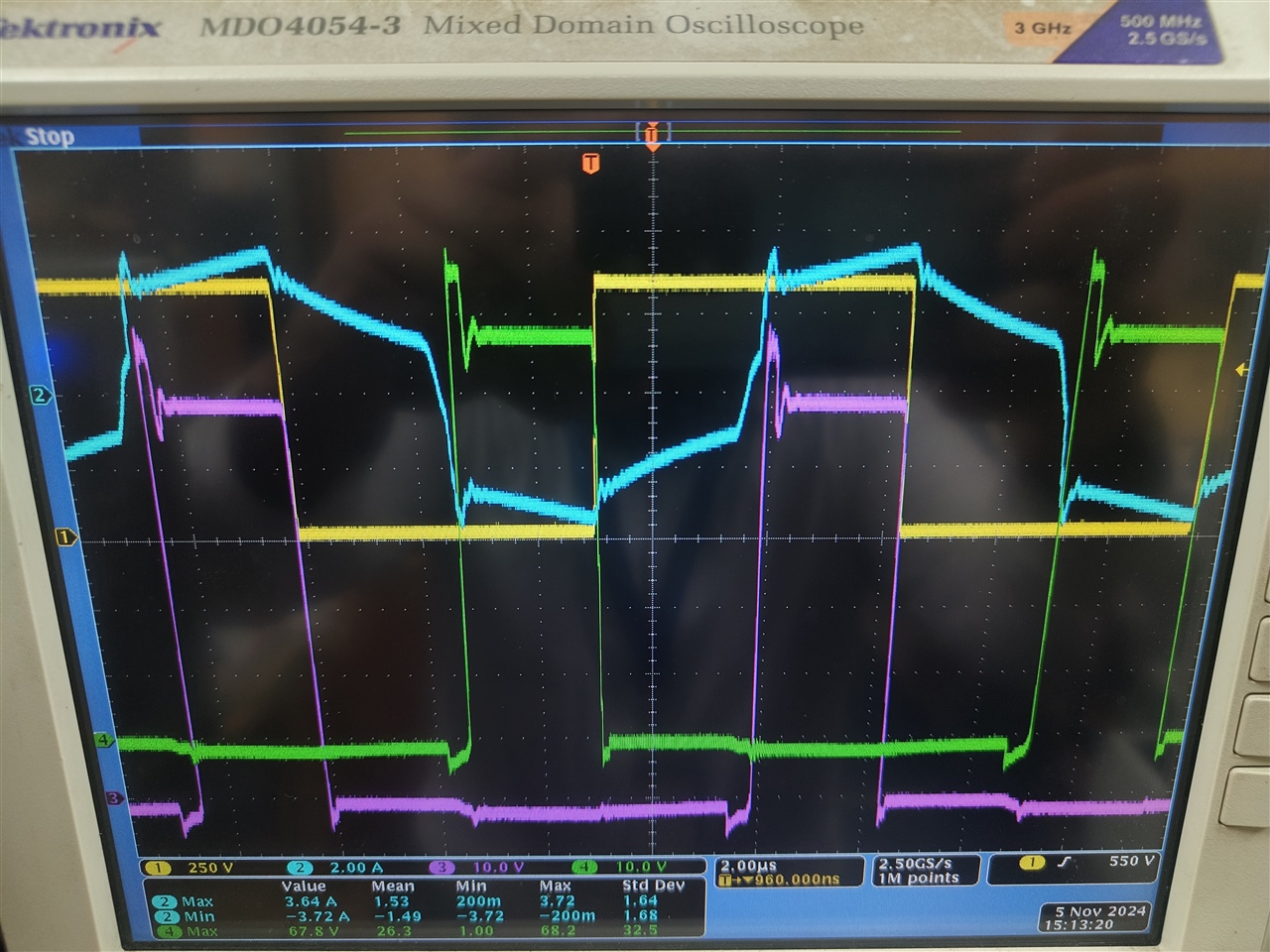

Testing using SiC MOSFETs

Scenario: Vin:810VDC, load : 43Adc

Below are gate drain source of primary MOSFETs. Resonant inductor is not being used. Transformer leakage inductance: 22uH, turns ratio : 27, output voltage: 23.5VDC. DCM pin is connected to ground. CS filter : 1K, 1nF. Fixed delay approach. Adaptive delay is grounded.

Blue : primary current

Purple: synchronous FET F

Green : synchronous FET E

Yellow: A drain source

Yellow: B drain source

Yellow: C drain source

Yellow: D drain source

1. C and D drain source waveform looks proper square wave, why not A and B ?

2. I'm Operating synchronous FETs now in CCM mode. I understand DELEF delay resistor might be little off for now, that I will try to adjust.Earlier Even in diode mode I had leading edge current spike issue. How to troubleshoot or remove this ?

3. As per excel calculation, the transformer ring might disappear of I reduce DELAB DELCD values. But if I add Shim. Inductor, the DELAB DELCD values are increasing. Is it ok ?

4. What more can be done to improve this design? Kindly assist.