Tool/software:

Good Morning,

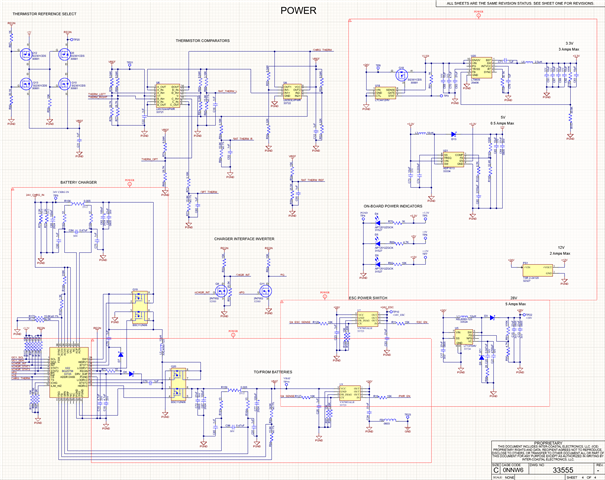

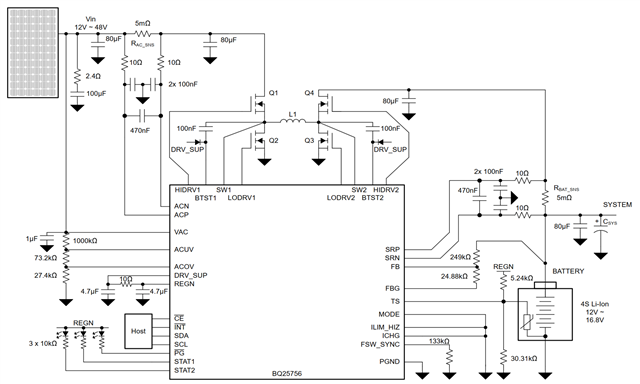

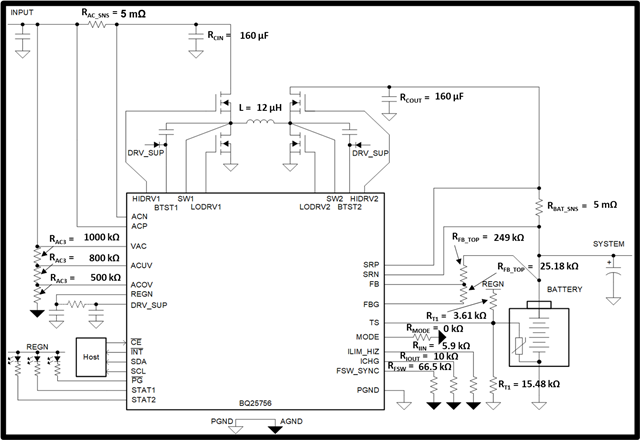

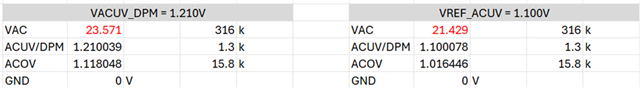

I have 75 CCAs with the BQ25756 handling battery charge (preferably stand-alone when the processors are off). In approximately 50% of the CCAs, I have run into an issue where the battery appears to be boosted and back powering the input supply when the input supply is disconnected. Referencing the sample circuit on page 71 of the datasheet, I am seeing the following results on the CCAs that are acting unusual (the other 50% are behaving exactly as would be expected and the problem is not intermittent):

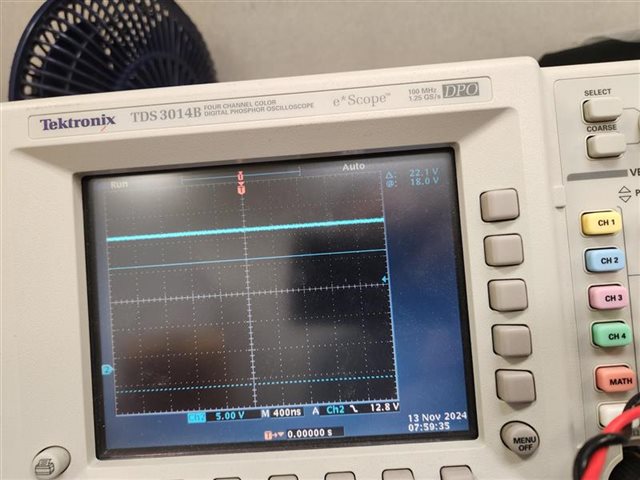

- Battery Voltage = 22.2V

- VIN = 23.5V

- Q4 Drain = 22.2V

- Q4 Source = 21.5V

- Q1 Drain = 23.5V

- Q1 and Q4 have a PWM with a low duty cycle present

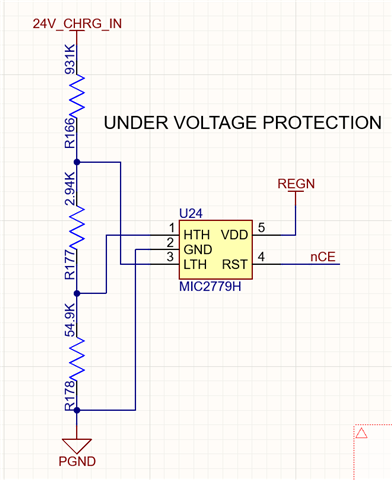

- REGN = 5V

- STAT1 = 0V

- STAT2 = 5V

The following register results are on the I2C when the problem is occurring and the processors are communicating

- Reg 17 = 0xC9

- Reg 19 = 0x20

- Reg 21 = 0x2B

- Reg 22 = 0x80

- Reg 23 = 0x00

I can get the back-feeding to stop by performing any of the following:

- Disconnect the Battery

- Increase/Decrease the thermistor temperature outside of threshold

- Set Reg 17 to 0xC8

- Add a large load to the input source

When I do any of the above 4 actions, the BQ25756 stops charging and powers off (REGN = 0V). I originally believed that the device was entering reverse mode; however, after observing the REGN at 5V and the registers reading Full Charge Mode (CC) while REV_EN =0, I stopped believing this to be true. I am concerned because 50% of our lot appears to be performing as expected while 50% seems to be failing in the same manner. If a copy of the schematic for the use case or pictures of the signals will be of any assistance, please let me know and I will provide them. Any assistance with this problem would be greatly appreciated.