Other Parts Discussed in Thread: , CSD19535KTT, CSD19532Q5B

Tool/software:

Hello,

My customer requests TI's review of the TPS23523 design.

Please review the following:

Q1. Please check to see if there is a problem with that customer's circuit.

Q2. The TPS23523EVM-863 user guide lists the current limit setting as 12.5A. According to the circuit design of the EVM, ICL1 = VSNS,CL1 / RSNS = 40mV / 2mohm = 20A. Please tell us how to calculate 12.5A.

Q3. The SNS pin of EVM is connected to VEE through 100ohm. Please tell us why this connection is needed.

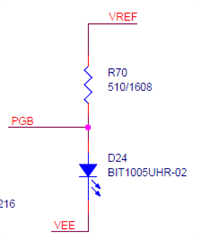

Q4. Could you please advise if the PGB pin connection circuit below is ok?

Q5. Based on 100W load, would it be okay to change the FET (CSD19535KTT) connected to GATE to the FET (CSD19532Q5B) connected to GATE2? For this, are there any additional factors to consider besides the power and current of the FET?

Thanks in advance.

JH