Tool/software:

Hi Expert,

My customer is using UCC5350, but clamping function couldn't work normally. here is the schematic and wave. please help to review

Br

Chi

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi Expert,

My customer is using UCC5350, but clamping function couldn't work normally. here is the schematic and wave. please help to review

Br

Chi

Hi Chi,

I do not see the wave. How do you know that the clamp is not working normally? Is there shoot through?

You should try to put a capacitor directly across VDD and VSS to protect the gate driver's output stage from transient overvoltage. Otherwise I see nothing wrong with your gate driver schematic.

Best regards,

Sean

Hi Chi,

is CH1 the CLAMP to VEE2 voltage? What are the other channels?

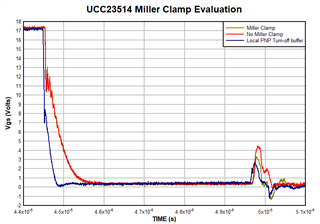

The clamp will help reduce the Miller injection, but it does not always solve the problem. In this case, you might have too much distance between the gate driver and the FET, and the inductance of the CLAMP loop is higher than its resistance.

Another alternative is to use a local PNP turn-off, which will minimize the turn-off loop length. Here is a comparison of the Miller spike with no CLAMP, with CLAMP, and with a local PNP turn-off. There is still a Miller spike, but the goal is to reduce the spike amplitude below Vth as much as possible.

Another idea is to add ~1nF of external Cgs, which will itegrate the Miller current into a lower, longer voltage spike.

Best regards,

Sean