Tool/software:

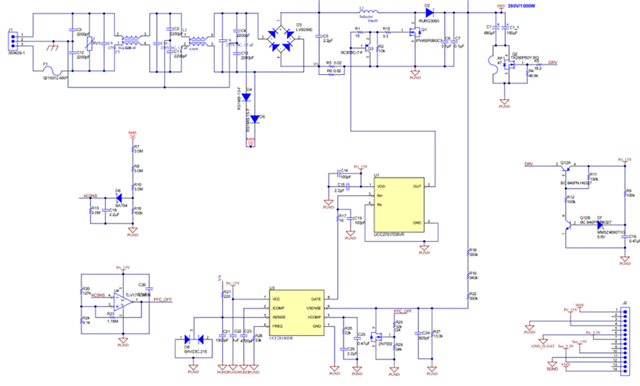

PFC工作环境:网侧220V市电输入,380V输出,设备为无线充电设备发射端,UCC28180用作boost pfc供电,设备满载功率为800W,电路可参考下图

问题现象:在设备满功率运行时网侧出现短时低穿,将PFC MOS击穿,经过后续复现,捕捉到PFC电感的电流波形ch4以及PFC输出电压波形ch1,可见此时有持续8ms左右的40A电流通过

问题点:1、查阅UCC28180数据手册以及论坛类似问题后,猜测该大电流出现的原因是因为此时VCOMP引脚电压在低穿发生时抬升,低穿结束时由于VCOMP过高导致UCC28180内部电流环增益M1过大,所以此时网侧恢复会导致输出有大电流,基于这种情况,请问如何进行修改避免出现MOS烧毁?

2、电路设计中的网侧过流保护ISENSE在低穿发生时未生效,目前不知道为何,望给出建议。