Tool/software:

Hello,

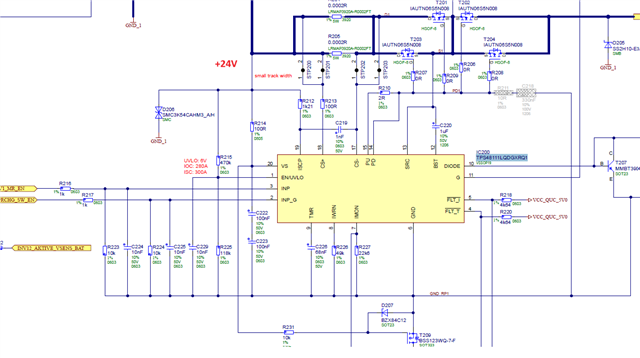

we are using TPS48111LQDGXRQ1 IC as a high side switch for motor drive.

Currently ECU is taking very high current in sleep mode.and after investigation we found this IC is taking much current in sleep mode. With INP pin gate driver is in disable state.

EN/UVLO pin is at greater than 2.2V almost 6V.

as per datasheet if we have to put this IC in shutdown mode then need to provide <0.3V to EN/UVLO pin so that IC would only consume 1.6uA.we ties this pin to GND ,still current consumption is high.

Could you please what could go wrong in this case?