Other Parts Discussed in Thread: INA219, TPS25947

Tool/software:

Hi team,

So after the GREAT support i got here https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1423648/tps631000-searching-for-a-bidirectional-dcdc-smps/5458962?tisearch=e2e-sitesearch&keymatch=TPS61289#5458962

I have returned with a more or less finished schematic to check if all is ok.

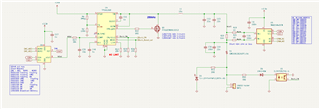

so F1 is rated for 3A hold current and my desired continuous current is 2A (3A maybe later if all is ok and the IC is not to hot)

Both the SMPS control pins are toggled by a MCU, it also reads the INA219 and controls the DAC . There is a opto coupler that acts as an emergency disable for the SMPS in case it is ON for some reason when i cell in inserted in reverse ( it should not be but it is a safety mechanism) . There is enough series resistance to not overdrive the MCU pin of the opto is active.

D6 is probably redundant since the opto coupler can handle 6V in reverse voltage.

Addresses are set on a higher LVL schematic ( there a multiple blocks like this on the 24V bus, there is also a INA219 on the 24V bus that will sum up net current going in and out of the board and some bus protection like a fuse.

Vref is 1V6 in schematic but we can adjust it, i am heavily considering going with 1V8 since it is a way more common voltage value.

From what i understand in the datasheet with Vhigh stuck at 15-25V and Vlow in the 2.5-4.5V range my switching frequency will stay constant at 250kHz. all inductor math was done with this value only.

1 Output and input capacitance are from EVAL board val;ue scaled for my current , there is no calculator or datasheet formulae, EVAL is at 10A and i need 2A so i more or less did a /5 on the capacitance.

There seems to be enough free space and i could add a few more footprints and decide to populate or not..... ( this in on Vlow )

2 On Vhigh ill do the same and in a way all blocks share capacitance so i am not sure, considering adding some big caps between adjutant blocks. What do you think ?

3 R20 Current limiting resistor , 20k is for full 20A , form datasheet. Regarding the formula i am not sure what you mean by Valley current.

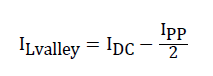

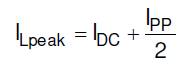

Using provided formulae from TI in boost mode we have:

| Inductor_dc_current_max[A] |

5.56 |

| Inductor_peak_current_max[A] | 1.63 |

and in Buck mode :

| Inductor_dc_current_max[A] | 0.67 |

| Inductor_peak_current_max[A] | 8.10 |

Those are the largest value given the worst possible conditions for buck and boost mode.

and if i apply the inductor saturation current formula we get 9.6A , the inductor can handle that + safety margin larger the inductor tolerance.

What current do i use for the current limiting resistance for both buck and boost mode ? For buck it is the peak* so i assume 8.1A, and for boost what is this valley current ? Is it peak + DC ?

Or should i go with 10A just to be safe and see what value i get from there? -R20=40k in this case

NOTE the (k) in the formula makes it VERY confusing since initially i though Rlim is in kohm and ended up with 40Mohm and that was very unrealistic, after i tried for 20A i figured it out

4 D1 is mostly for debug + place to put measurement test points

5 Any obvious mistakes on the schematic ? Or is there any things that i could do better and cough your attention?

6 For preventing damage when a cell is placed in reverse do you have any small size solutions better then the fuse?