Tool/software:

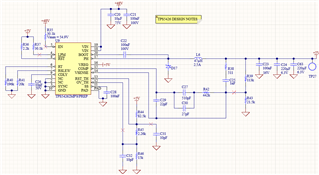

Some design parameters:

- Vin, min = 40V

- Vin, typ = 48V

- Vin, max = 55V

- Vreg = 5V +/- 1%

- Iload, max = 2A

- ∆VIN 1% of Vin

- Vreg_RST = 92% of Vreg

- Vreg_OV = 106% of Vreg

- Vreg_UV = 95% of Vreg

- ∆VReg = 5% of Vreg

- PORdly = 10ms

- Fsw = 500KHz

We tried a slew of things on a "bad" board including (but not limited to:

- Increase soft start (no change)

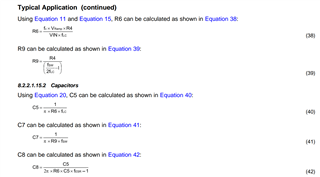

In the end reducing threshold resistors (R1, R2, and R3) by a factor of 5 solved all issues. R1, R2, and R3 originally added up to 100k but now are at 20k. The datasheet has two different statements on this - one says they should add up to less than 200k and another says they should add up to 100k. The theory here was there was noise on the threshold values and increasing the current increased our noise threshold (just a guess).

Thank you for your help.