Tool/software:

Hi,

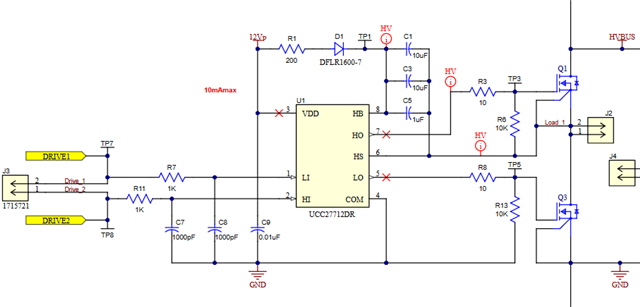

I am trying to implement a circuit using the UCC27712 based off of the PMP23338B reference design.

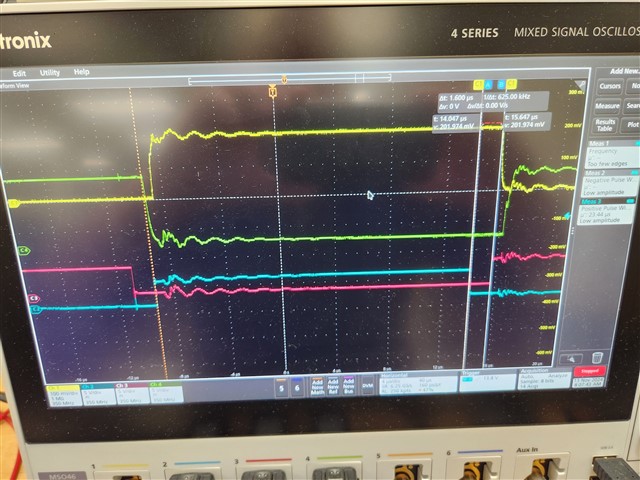

In the attached scope shot

Yellow -- HO referenced to HS (ignore voltage scale)

green -- LO

Blue -- HI

Red -- LI

It appears that the delay to the rise time of the output signals matches the data sheet (100ns). However, the fall time is 1.6usec when it should be 100ns?

In light of this, I need to go back and look at the timing on the PMP23338B reference design when I have time. We implemented the design and noticed a lot of switching noise that needed more investigation.(off topic).

Regards,

John