Tool/software:

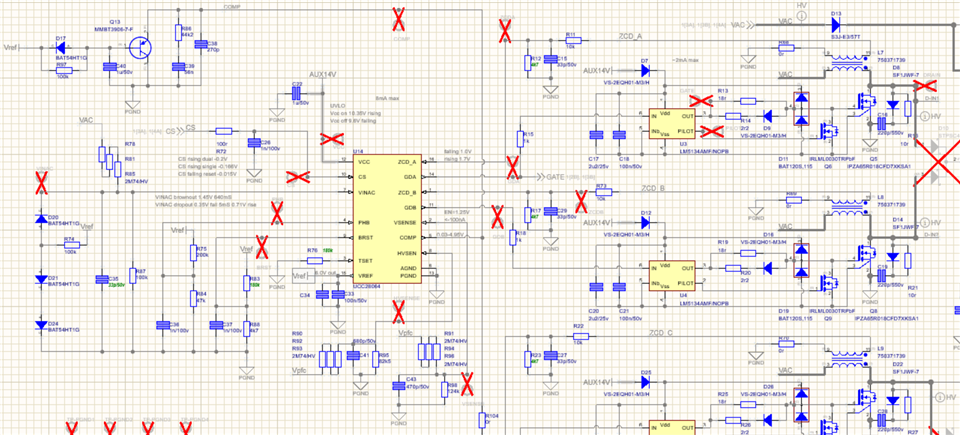

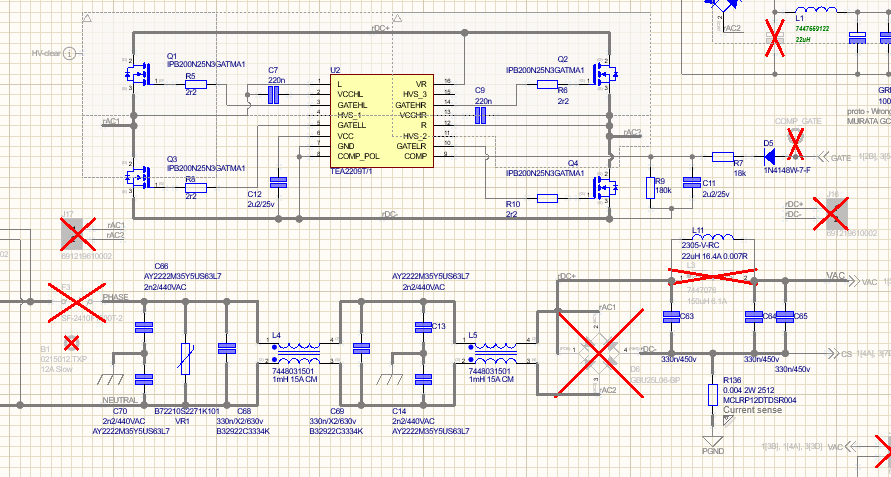

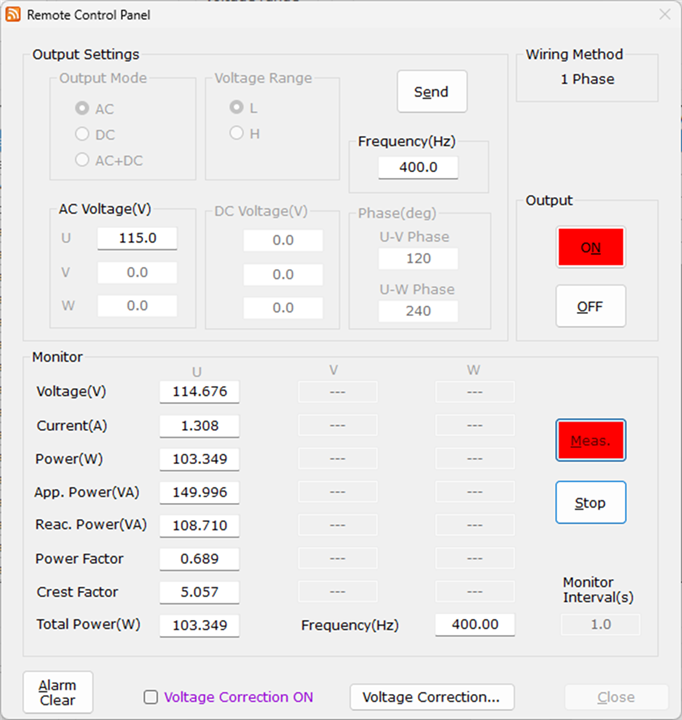

Hi - I've got a PFC circuit running taking a 115V AC and generating 400V DC. Target output is around 700W and I will be doubling the circuit up once everything is running sweetly to get 1.2kW+

At the moment I'm getting awful PF figures (of around 0.3 at no load, peaking at 0.7 at about 200W and dropping back to about 0.5 at 500W+)

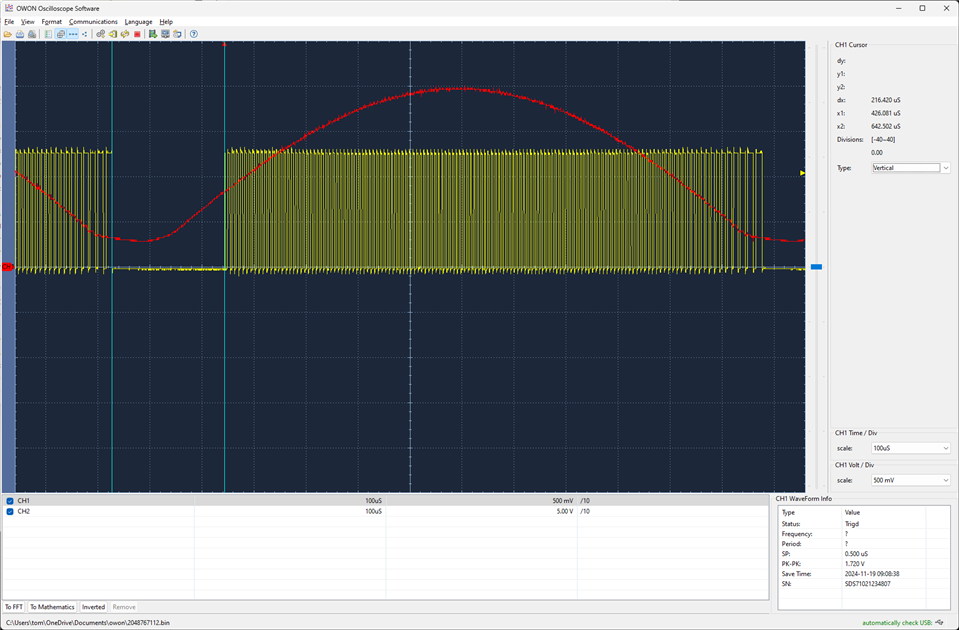

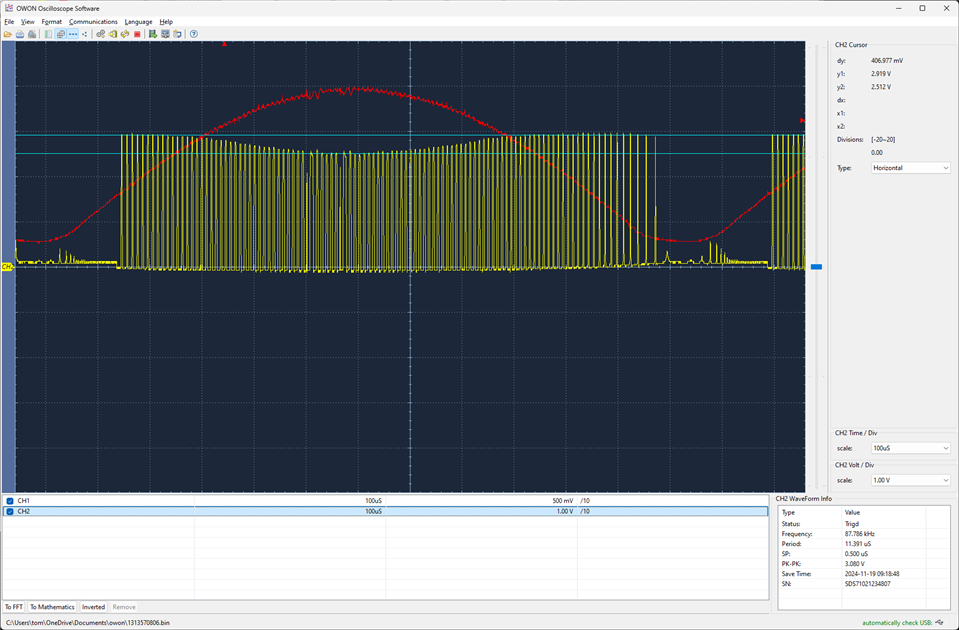

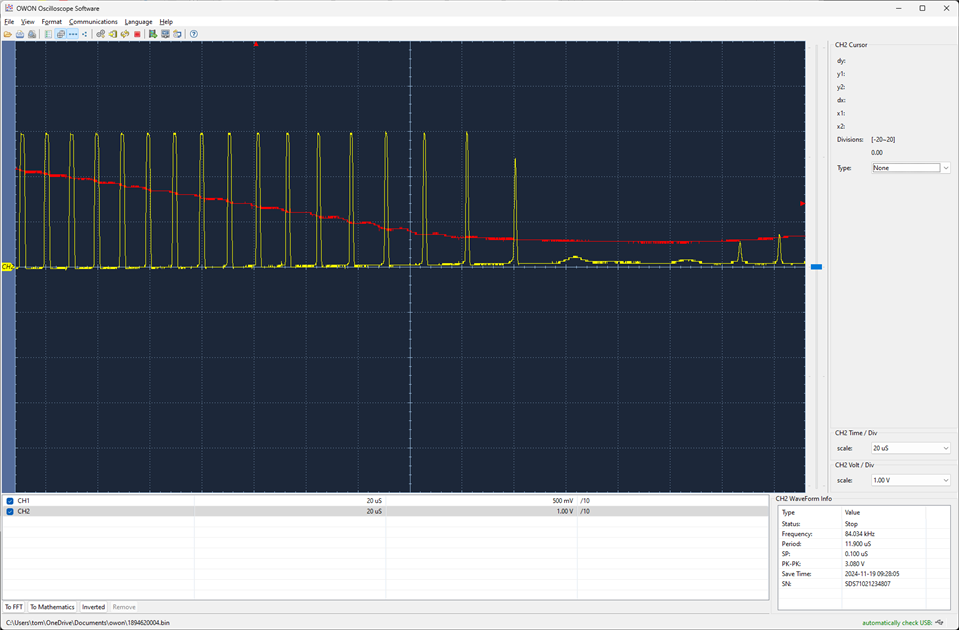

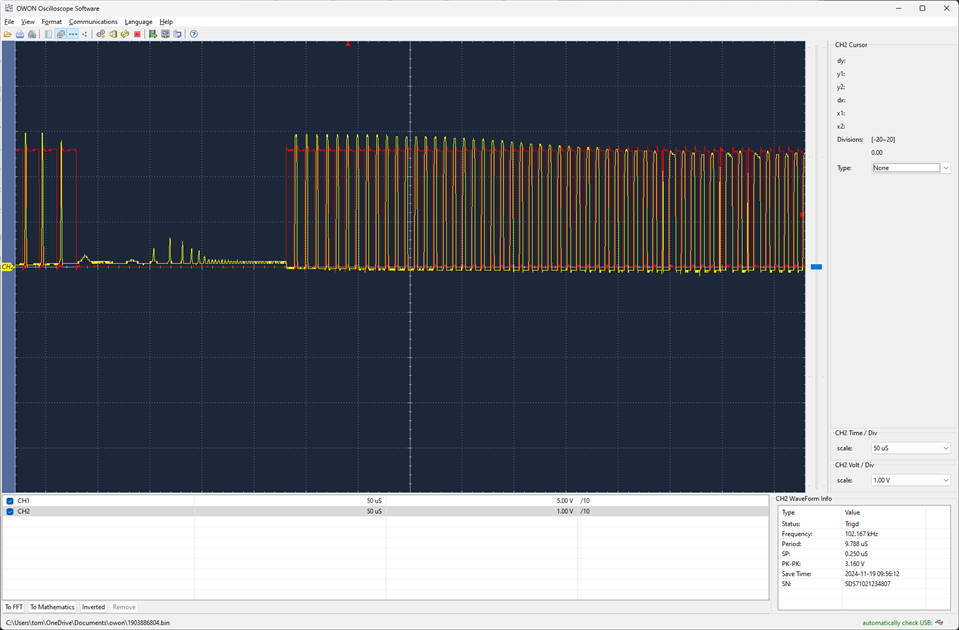

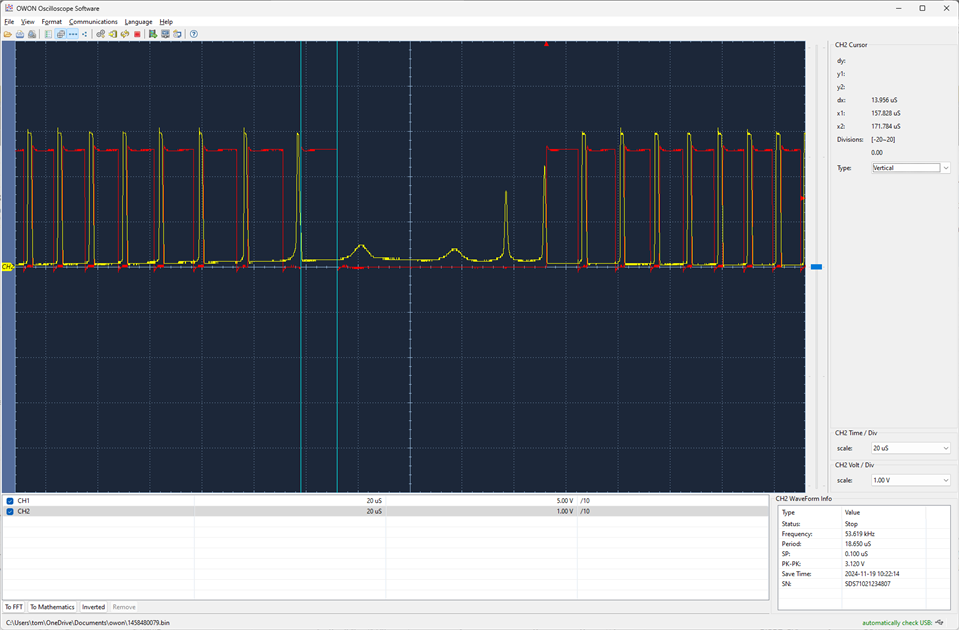

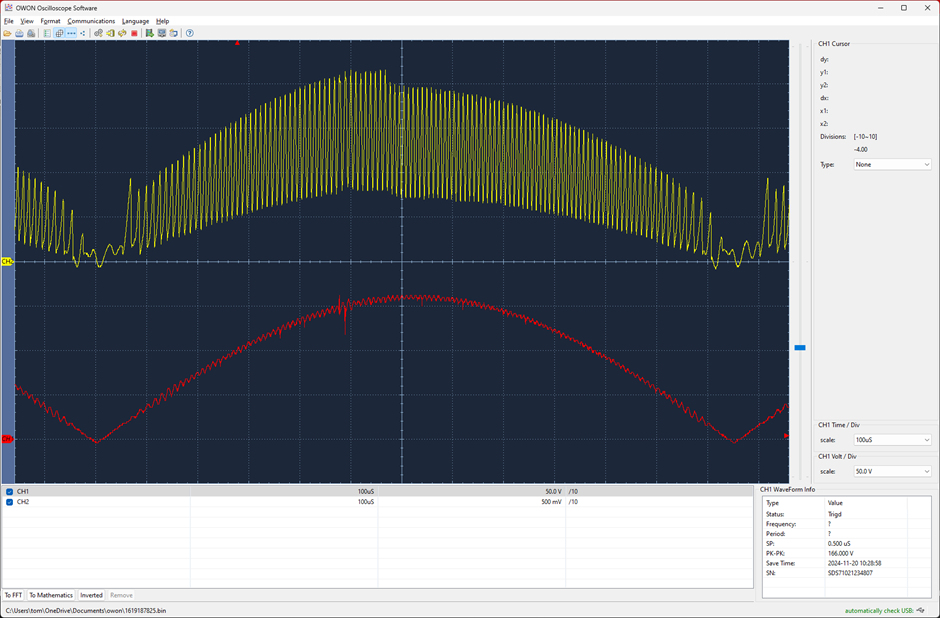

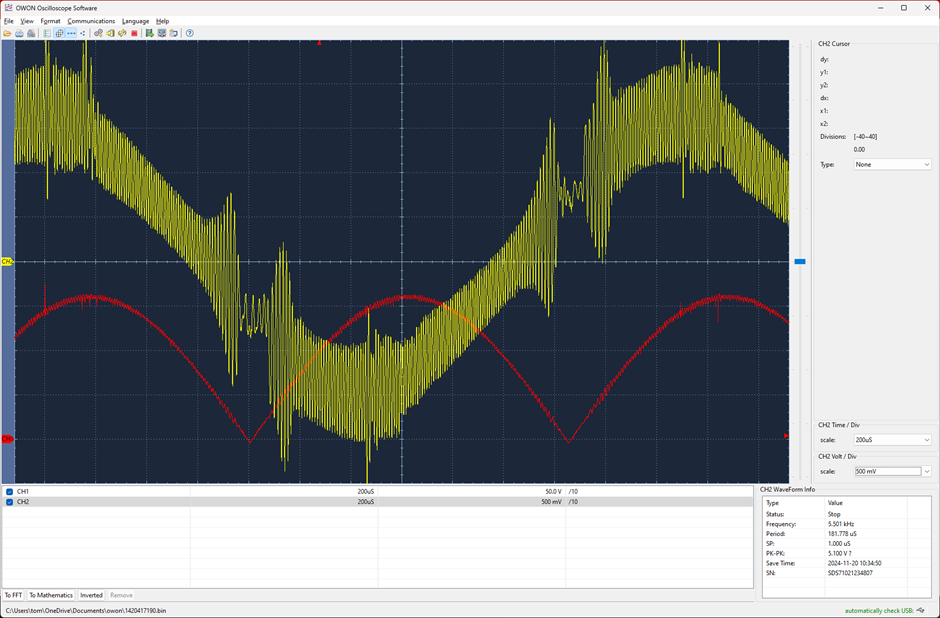

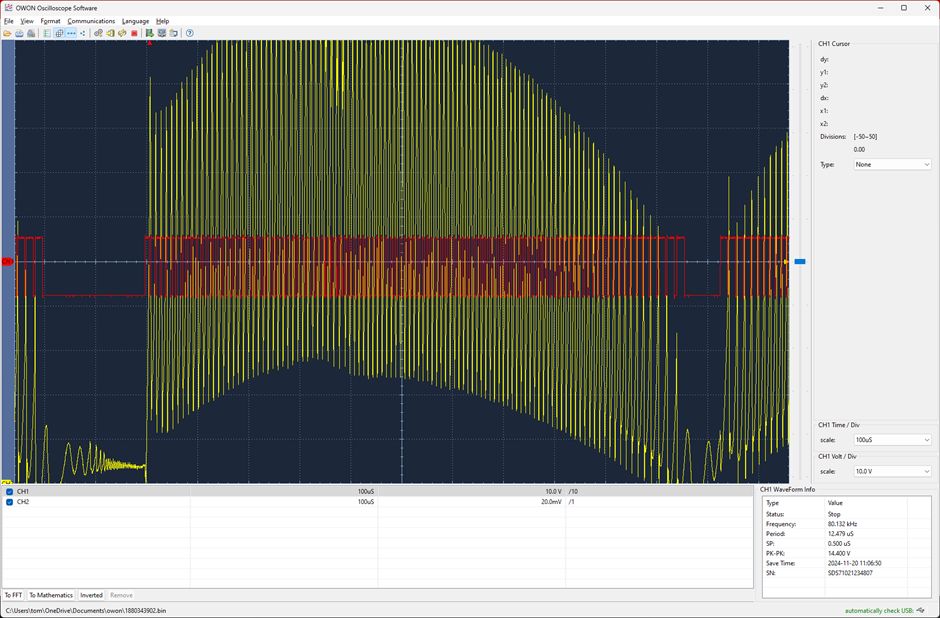

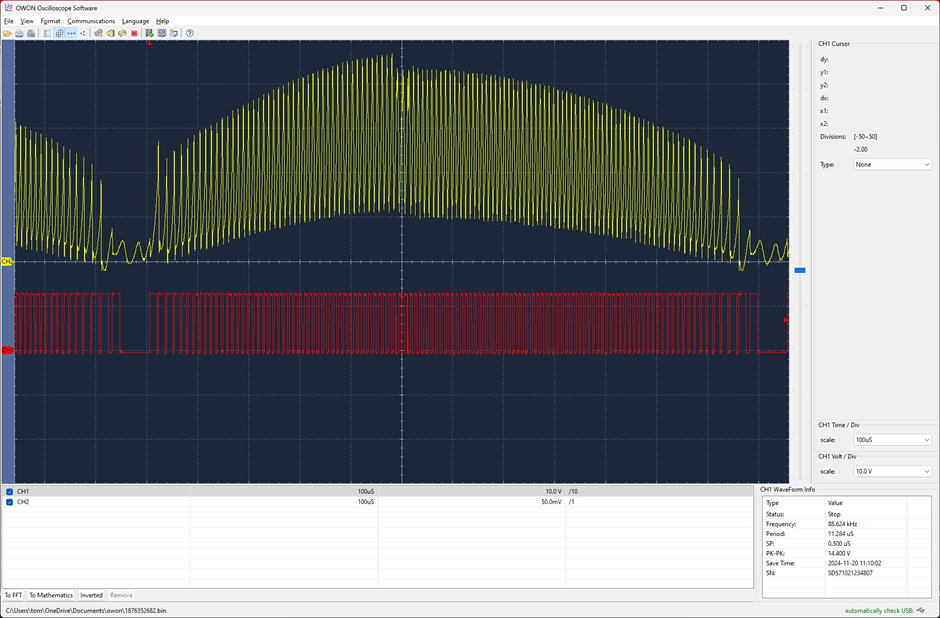

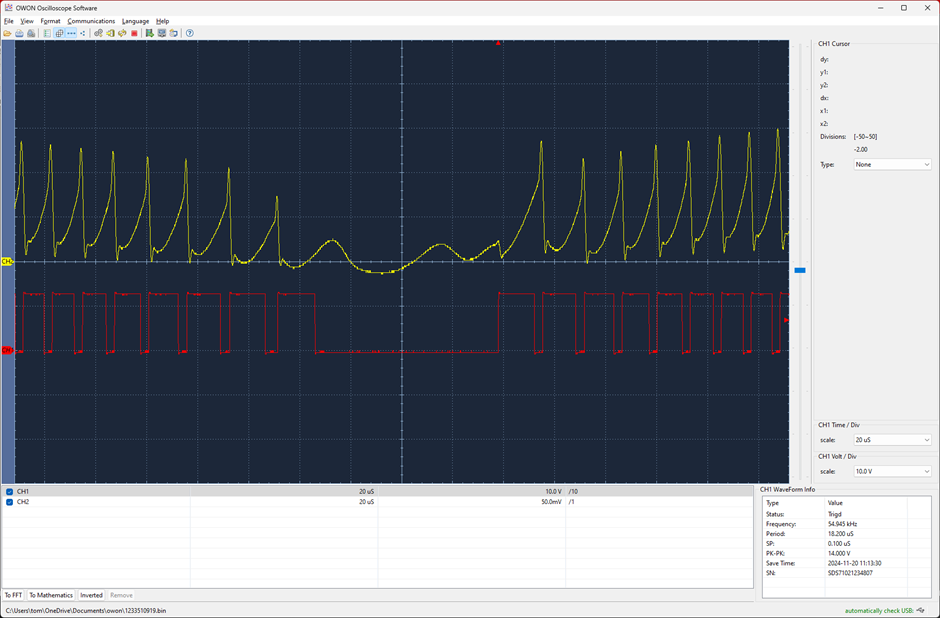

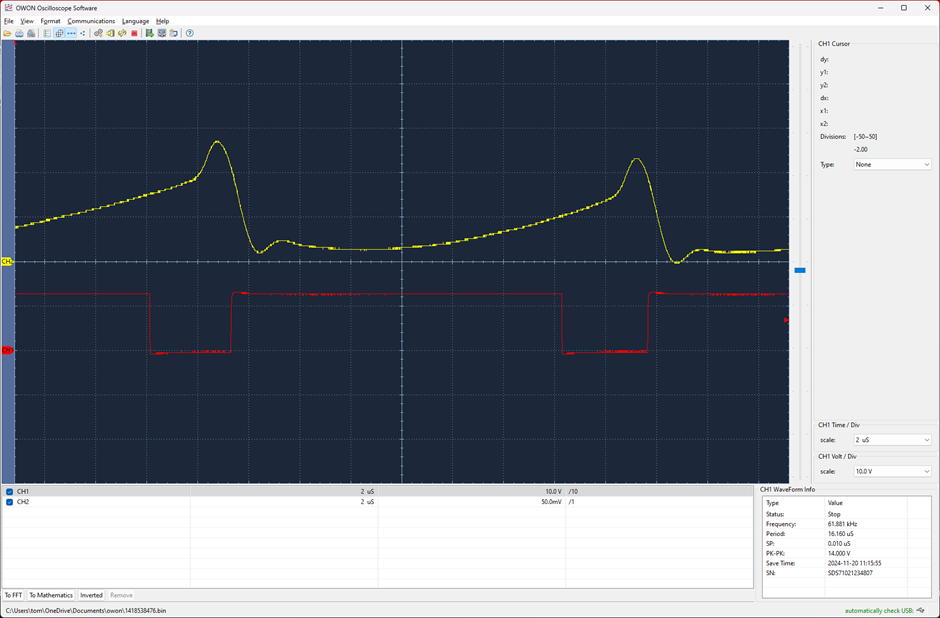

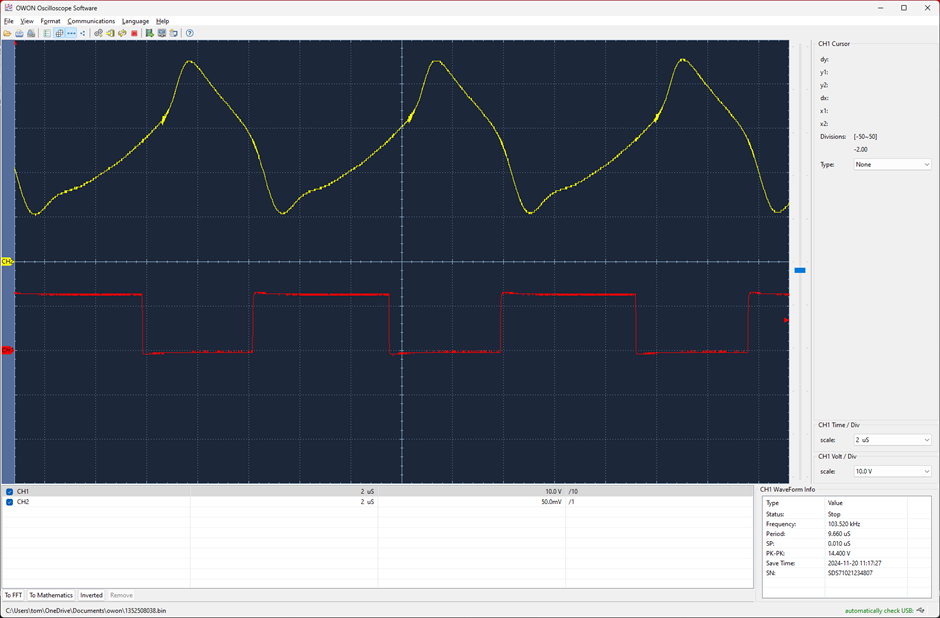

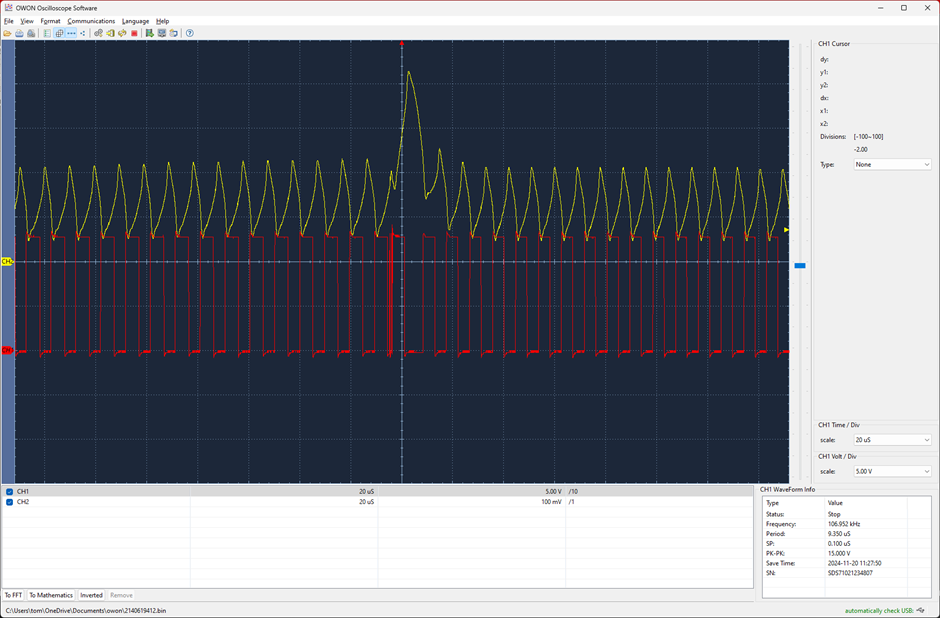

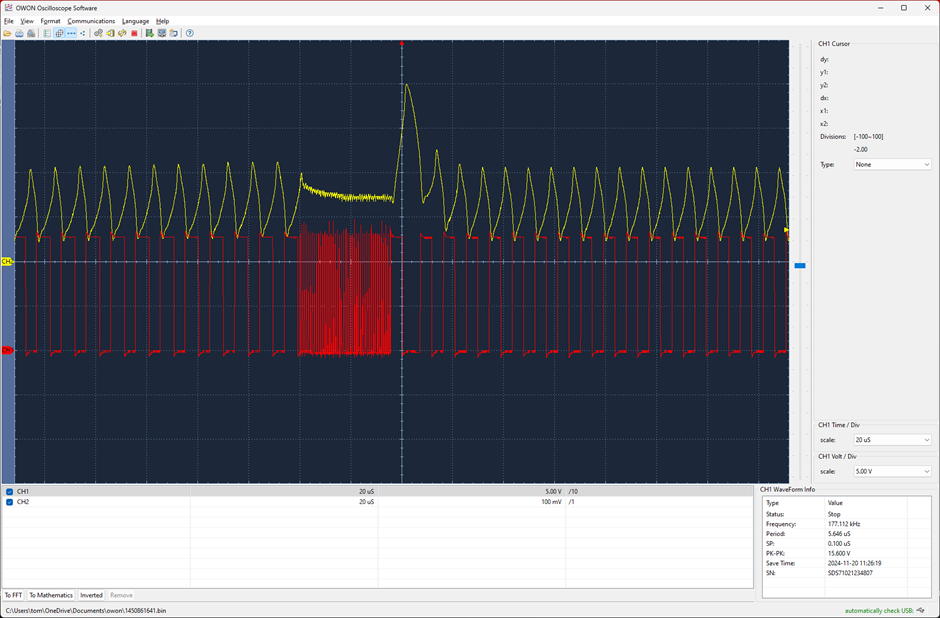

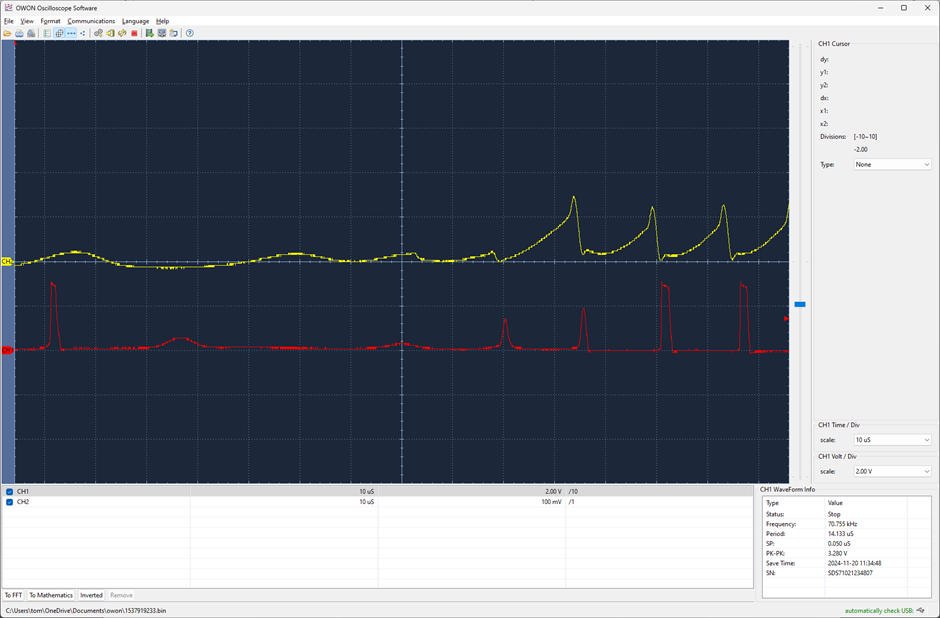

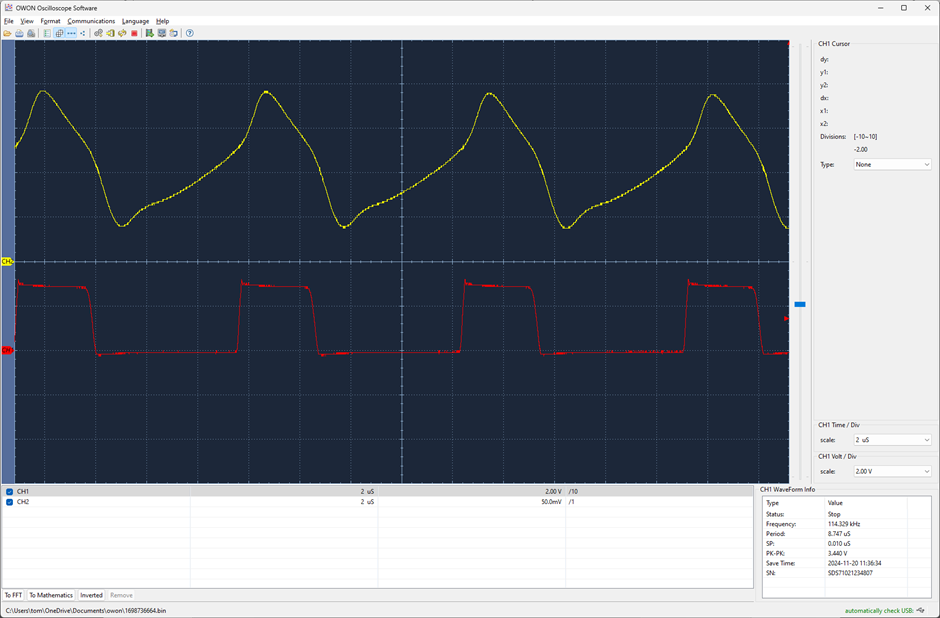

Obviously the intention is a near-unity PF, so something isn't right. Upon analysing the switching pulses, when the VINAC signal drops around 0V, the GDA and GDB outputs both stop switching and re-start again when VINAC rises on the next half-cycle. The switching timing is fairly steady during the half-cycle when they are active and you can see it varying the on/off times as VINAC rises and falls. (My test load is 100% resistive at the moment - a bunch of heater elements keeping my feet warm).

Should this stop-start be expected at the 0V points, or should the switching continue throughout the cycle? At the moment they are off for about 20% of the time. And significantly as the switches come back on, they start in-phase with each other and do not settle into interleaved mode until the waveform is at around the peak, so we are only running in interleaved mode for about 40-50% of the time. Is that also to be expected? That the two phases are in-phase to start with?

I've tried with/without the funky diode arrangement for low-VINAC distortion improvement. With, no improvement. I've also tried playing around with enabling and disabling both BRST and PHB trigger points. All with no effect.

My inductors are currently 250uH, and I'm wondering if they are too small as I've had to increase switching freq (increasing RTSET) to prevent current walk-up. But would too-small inductance here prevent the switching at low VINAC? Would putting a 100uH in series with them be an easier/sensible solution rather than re-winding the custom magnetics?