- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello,

I am an FAE at a distributor that handles TI products.

I received the following inquiry from one of my customers.

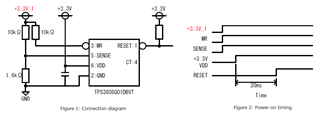

The connection will be as shown in Figure 1, and the MR and SENSE signals will be controlled by a signal generated from a separate system, +3.3V_1.

I am considering a circuit as shown in Figure 2, where the separate system, +3.3V_1, rises before the +3.3V applied to VDD.

(Question)

Will the device operate without any problems with this power-on timing?

Also, is there a risk of the device failing?

Best regards,

Hi Kaji,

The power up sequence should not be an issue since the MR and SENSE pins does not have dependencies on the VDD. There should not be any risk of failure. I do have a couple of comments though.

Jesse

Thank you for your reply.

Based on your opinion, my customer contacted me to say that he will use the MR pin in the open.

So, just to be sure, my customer would like to confirm the following:

If voltage is applied to the SENSE pin when VDD is not being supplied, will this cause damage to the device, such as latch-up, and cause the device to become damaged and stop working?

Best regards,

If voltage is applied to the SENSE pin when VDD is not being supplied, will this cause damage to the device, such as latch-up, and cause the device to become damaged and stop working?

As long as the voltage applied to the SENSE pin is within the tolerance of the pin, No damage will occur.

Jesse