Tool/software:

Hello.

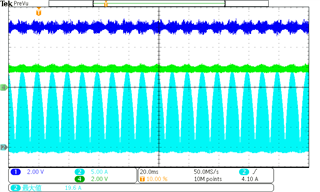

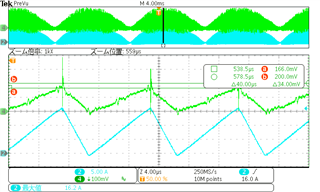

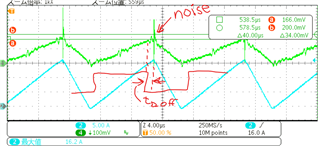

To allow the UCC28064A to operate in continuous single-phase mode, the PHB input was connected to VREF to disable phase B operation. Also, the coil is disconnected and the ZCDB signal is not generating anything. Although it is operating in single mode, I have two questions.

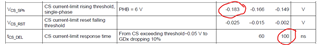

The first is that the peak current limit threshold on the CS pin input has not changed from dual mode (0.2V) to single mode (0.166V). I am aware that the threshold is 0.2V at startup and the threshold changes to 0.166V after 14 line half-cycles of Vinac.

On the current board, the current detection resistor is 12mΩ and the peak current is calculated to be 16.6A (at startup)/13.8A (at steady state), but when I operate the board on the actual device, the peak current is 16.6A at both startup and steady state. Is there any way to resolve this?

Second, I would like to know how to determine the optimal Rtset in single mode.

thanks.