Tool/software:

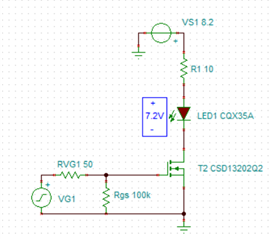

Working on a new project and would like to design a simple LED driver that will make an LED blink at 10 kHz. After reading some online application notes I found this simple circuit that I think will suffice for my needs:

However, rather than a BJT, I would like to control a switch through a function generator that will turn on/off a N-channel MOSFET. I made a porotype of the above circuit with a IRL2703PbF from International Rectifier and it seems to have worked adequately (other than the MOSFET getting fairly warm after 10 ish minutes of operation). I would like to turn my prototype into a PCB using SMD components and was hoping to get some feedback in if I need to consider more than just the SOA, VGS, and power dissipation P = RDS(on)2ID to pick an appropriate transistor for this application…

Specs of my expected operation conditions:

I will supply the voltage (7.2 V) and current limit (ID = 0.1 A) the LED directly using a separate DC power supply.

The gate of the MOSFET will be directly connected to a function generator (50 Ω output impedance) that will supply 0-5 V square wave with 10 kHz (or 100 µs pulses) modulating frequency with 50% duty cycle. (I.e., VGS = 5 V when ON and 0 V when OFF.)

I am thinking of using the CSD13202Q2. I have done some example computations of parameters below to check for "appropriate" working conditions.

From these specs and using the Fairchild/On Semiconductor FDV305N MOSFET as an example I expect (attached datasheet):

P = (0.1 A)2 * 0.22 Ω = 2.2 mW << 350 mW absolute rating

VGS(ON) = 5 V >> VGS(th) = 1 V

VGS(OFF) = 0 V < VGS(th) = 1 V

From the SOA figure (below), I expect VDS < 1 V as the LED will drop the 7.2 V applied by the power supply, ID = 0.1 A, and pulse modulation of 100 µs… I am well below the RDS(ON) LIMIT of the plot and in the safe operation range (I think).

Additional considerations:

Since I am directly using a function generator to supply the gate voltage and current, do I need to put a resistor between the gate pin and function generator? If so, is this for power dissipation and/or current limiting purposes?

Do I need to worry about the power dissipation at the gate of the MOSFET? I feel like since this is such a low power operation that I do not need to worry about that.

Do I need to worry about the the bias current needed for the gate (IG)? Based on some technical notes I read, IG = Qgfm = 1.5 nC x 10 kHz = 0.0125 mA (which I expect the function generator to be supplying approximately 50 mA with my operating conditions).

Thank you for taking the time to read my post! I appreciate any insight/feedback in the parameters I need to consider when choosing a MOSFET for pulse based driving of an LED.