Tool/software:

Hello TI experts,

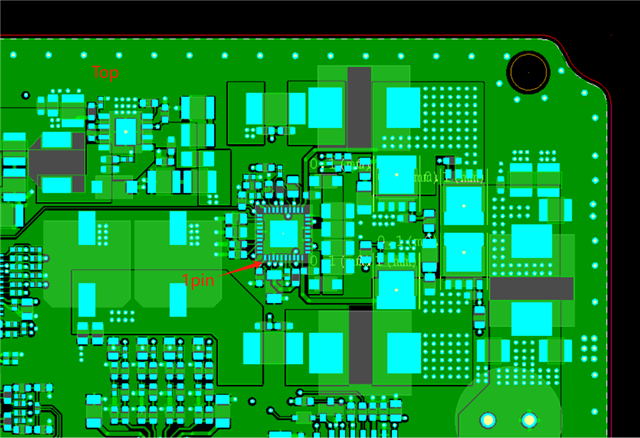

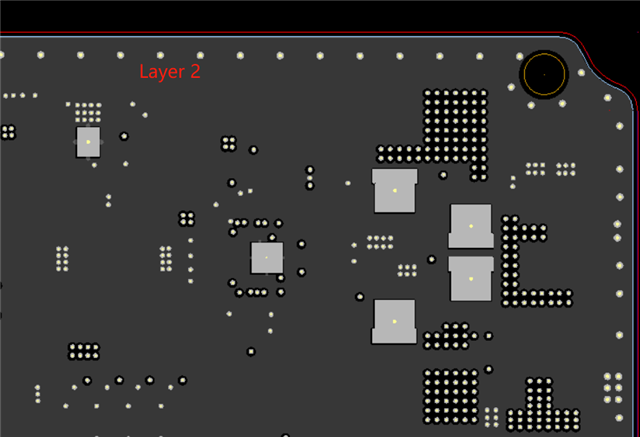

The project we designed used the LM5143+4pcs MOSFET dual phase architecture. input=16-32V ,output voltage= 14.4V, the current max 20A. The output current can reached 12A. Schematic as attached. There is no problem we mass-produced last year.

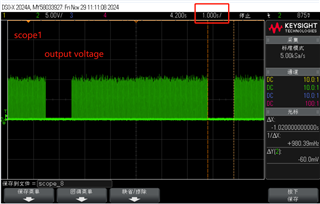

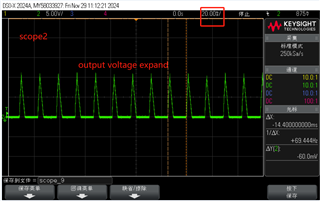

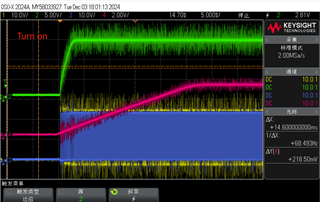

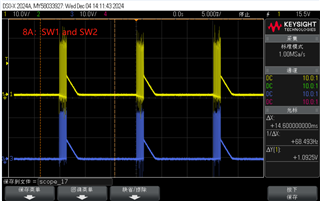

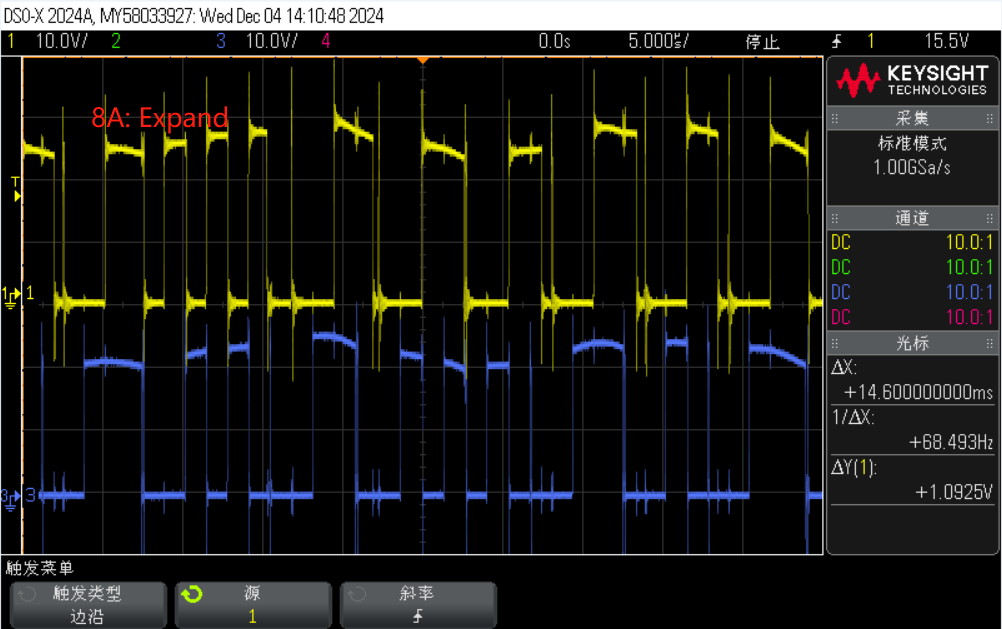

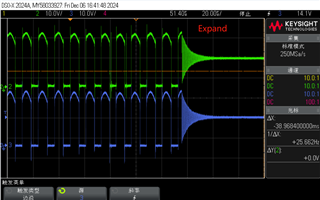

However, we recently mass-produced a batch and found that its output current capability has deteriorated,The component used is from the same batch left over from last year,the output current reached 5A the voltage not stability. please refer to the scope1 and scope2. The result seems the loop unstable.

I have verified the following steps.

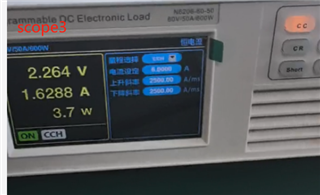

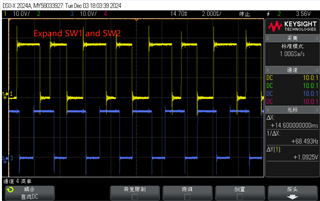

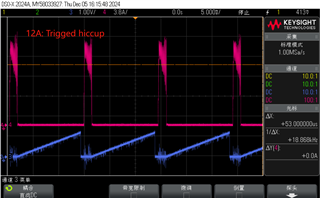

1.the Currently mass production:output current=6A begin unstable. please refer to scope3.

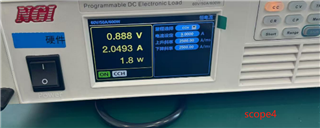

2.Change the 4pcs mosfet form the PCBA mass production last year, the output =9A begin unstable. please refer to scope4.

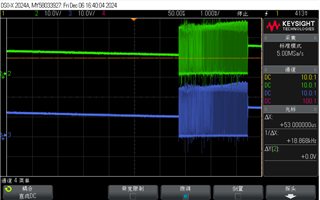

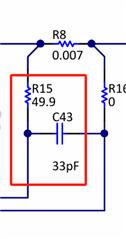

3.Populated the R65031,R65030 and C65051,C65050 can reached 12A no problem,Please refer to scope5. however the these 4pcs resistor and caps is also depop in production last year.

Please help analyze what difference is causing the abnormal performance of this batch of PCBAs. Looking forward to your reply.

Thank you.

BR Victor