Part Number: UCC256404

Other Parts Discussed in Thread: UCC25660

Tool/software:

Hi,

I am having some behaviour I can not explain with a UCC256404 under burst opeartion mode.

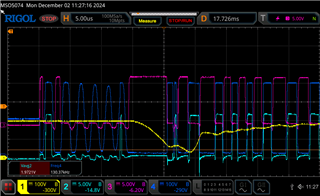

In the attached figure, CH1 is the resonant capacitor voltage, Ch2 the upper side gate, CH3 the lower side gate, and CH4 the MOSFETs Switching Node.

As it can be seen, when the controller starts a new burst packet, the first gate pulses start under soft burst mode, and the switching node seems to clamp when the input voltage rail is reached (which I guess is needed for the activation of the upper switch and the setting of the dead time). The swtching node derivative is close to 1V/ns when the voltage raises, however, as it can be observed the second time the switching node rises, the upper side gate is not turned on, but then it activates after the switching nodes resonates for some cycles ( the delay for the activation of the upper switch varies, but it seems it always happens under hard switched conditions). After this behaviour, i always get a long 5us low side gate pulse, and after some cycles it seems to return to normal operation. I have seen that if I increase the BMT level, the behaviour goes away, and I guess this is due to higher dv/dt voltages at the switching node at the start of the burst packages. My concern is that I can hear those switching events, and I also understand it puts unnecessary stress on the switches (the 5us pulse discharges the resonant capacitor resulting in an unnecessary high resonant current event). I could solve this issue by increasing the burst mode thresholds, but then I would affect ripple and cross regulation in an unregulated auxiliary output I have in the design.

My question is: is it not the dv/dt at the switching node high enough to ensure proper operation of the high side gate (>0.1V/ns)? I have monitored VCC, RVCC and upper side bootstrap supply and I could not see anything wrong (all seem solid and well above UVLO). Soft start pin remains at 3.5V during this event (no ZCS events).

Thanks!