Tool/software:

Hi Support Team,

We have some clarifications to seek regarding the recent PCN (Product Change Notification) for the TL431. Specifically, we would like to confirm the following points:

-

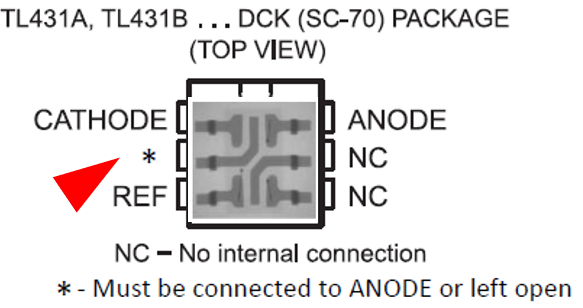

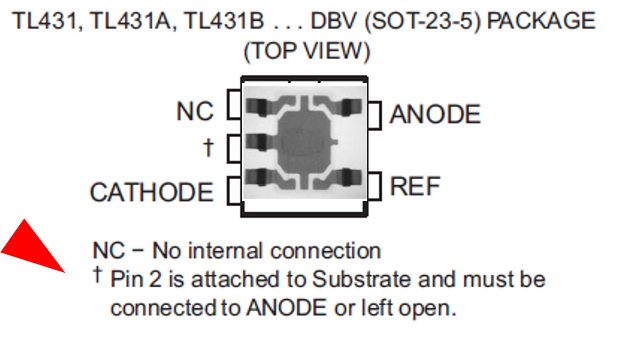

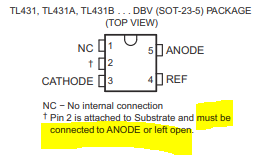

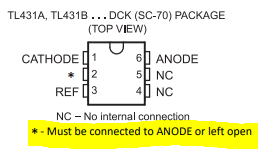

Impact of Connecting Pin 2 to CATHODE/REF:

-

Many of our applications involve connecting Pin 2 to both the CATHODE and REF terminals. Could you clarify what specific issues or problems may arise from this configuration under the new specifications? Are there any scenarios where this connection method could result in device malfunction or performance degradation?

-

-

Scope of the Change:

-

The PCN indicates a change in specifications. Can you confirm whether this involves only a change in the documentation or if there are internal modifications to the product itself? Specifically, does the new specification arise from an internal design change that might introduce issues when Pin 2 is connected to both CATHODE and REF, necessitating a change in usage guidelines?

-

We would greatly appreciate your prompt response as this will help us assess the necessary steps for compliance and application adjustments.

Thank you for your suppor

Thanks,

Conor