Other Parts Discussed in Thread: USB2ANY, EV2400

Tool/software:

Hello, I am using the BQ25756, which communicates with an ESP32 in standalone mode. I am facing two issues that are not functioning as expected:

-

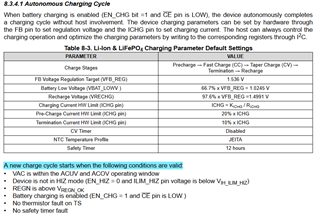

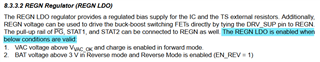

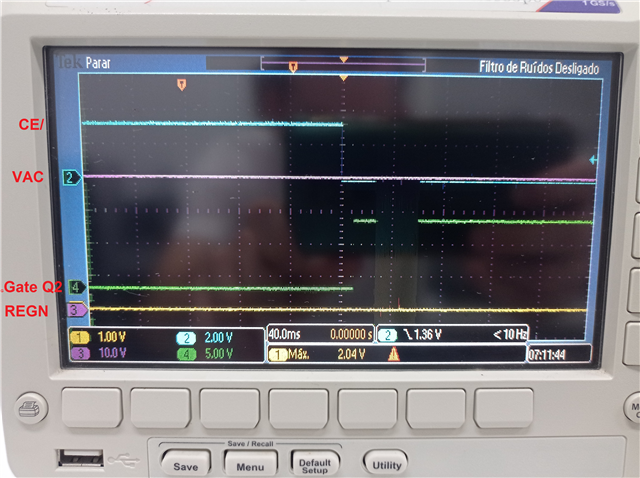

The input voltage is within the operational window (38V–60V). It was verified that the PG_STAT bit is being read as 1, and the CE/ pin is pulled LOW. Using hardware, it was confirmed that the voltage on this pin is 0V, and the EN_ICHG bit is being read as 1. However, the device is still not initiating charging, and the REGN pin remains at 0V.

-

The ADC converter seems to perform only a single conversion upon power-up and does not convert further. The procedure for reading was as follows:

- The ADC configuration was left unchanged, using the default settings (one-shot mode, 13-bit effective resolution, etc.).

- Conversion was enabled by writing

0x1to ADC_CONTROL. - Sequential reads were performed on the registers IAC_ADC, IBAT_ADC, VAC_ADC, VBAT_ADC, and TS_ADC.

- The values read were converted into their respective parameters according to the range specified in the datasheet, and the loop restarted at the first step (enabling the converter).

During testing, I added a check for the ADC_CONTROL bit to verify that it was enabled, and it was indeed being read as 1. However, the ADC_DONE_STAT bit was always read as 0, indicating that the conversion had not completed. Even when waiting approximately 1 second to allow for conversion, it still failed to convert. When the verification was removed and the loop was allowed to run continuously, the ADC still did not perform any conversion, even after waiting for over 1 minute.