Other Parts Discussed in Thread: UCC28019, UCC24624

Tool/software:

Dear Sir,

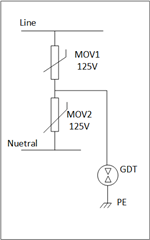

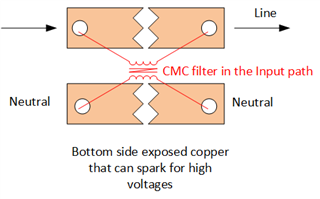

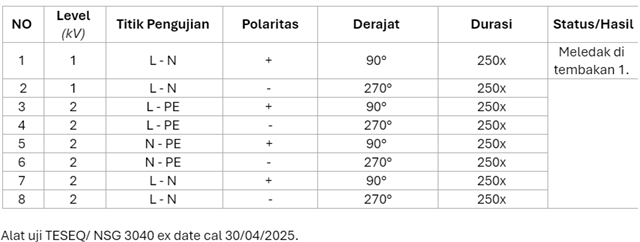

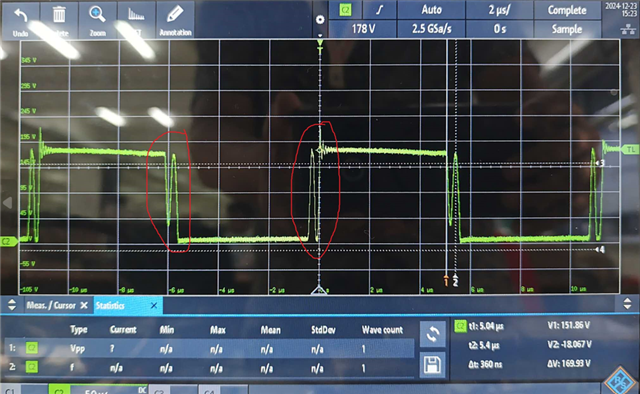

I have new issue with surge immunity for my charger for EV new design

the issue is when surge immunity test the POWER MOSFET for half bridge,POWER MOSFET soft start and PFC controller UCC28019 always damage ,please help me how to solve (throuble shoot) that issue.

There's the attached for schematic diagram and pcb design .

Thanks and Best Regards ,

Supardi

850W CHARGER EV 2024-12-11.pdf850W CHARGER EV 2024-12-11.zip