Tool/software:

Hi,

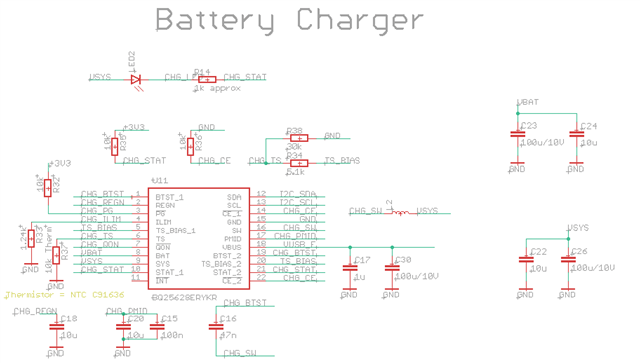

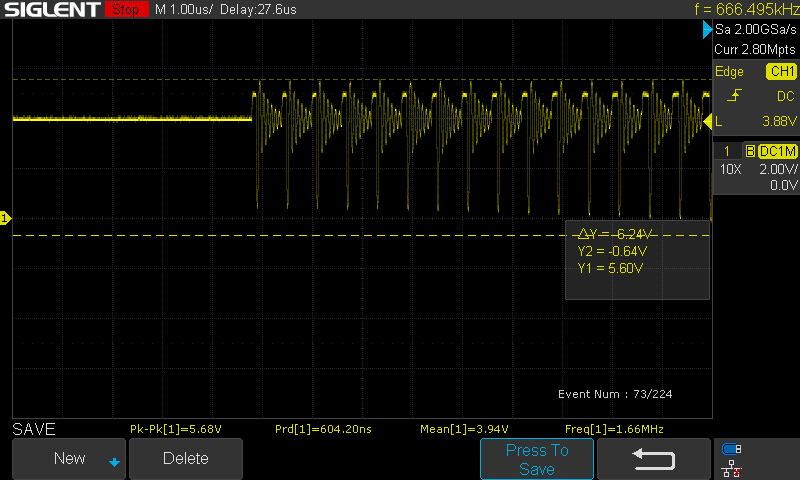

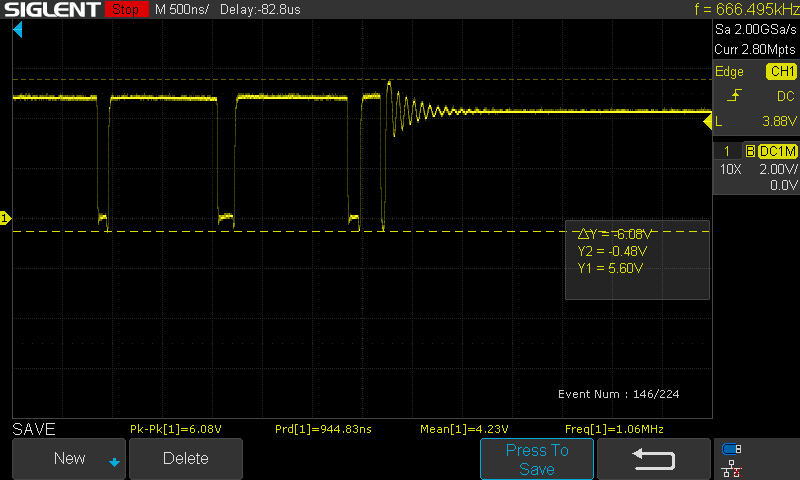

I am creating a custom design using the part. The charging, ADC, etc. functionality works well. However, at light loads (= battery fully charged or no battery) when the system draws about 50 mA from VSYS, VSYS becomes noisy, unstable and the output capacitors audibly buzz. It seems this might have something to do with the PFM mode being activated, but I explicitly disabled PFM (PFM_FWD_DIS = 1).

The status registers are as follows: Charger_Status_0: 00, Charger_Status_1: 0x14, Charger_Flag_0: 0x10, FAULT_Flag_0: 00

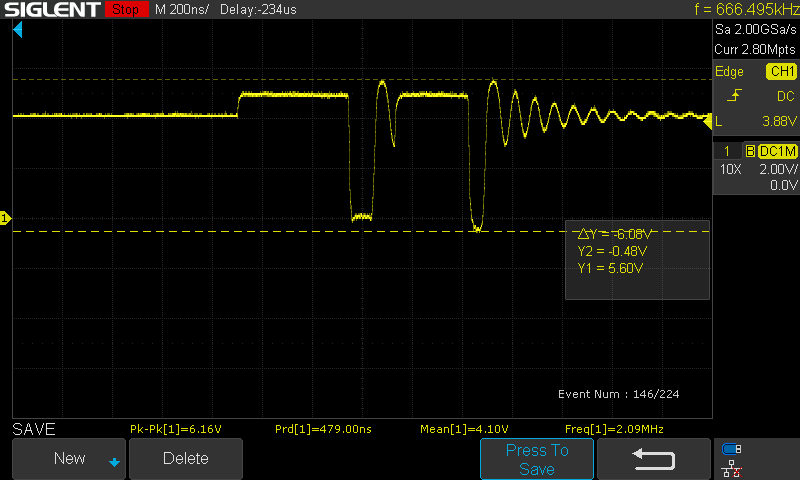

Charger Flag 0 reports (0x10) occasional "Entered or existed VSYS min regulation". I've attached the oscilloscope trace for VSYS below.

The ADC reports the following values, which all look reasonable: Ibus: 74 mA, Ibat: 0 mA, Vbus: 5.136 V, Vpmid: 5.136 V, Vbat: 4.208 V, Vsys: 4.230 V, Tbat 26 C, Tdie: 25 C

How can I ensure a quiet VSYS under no battery or fully charged conditions, please?

Thanks

Martin

VSYS

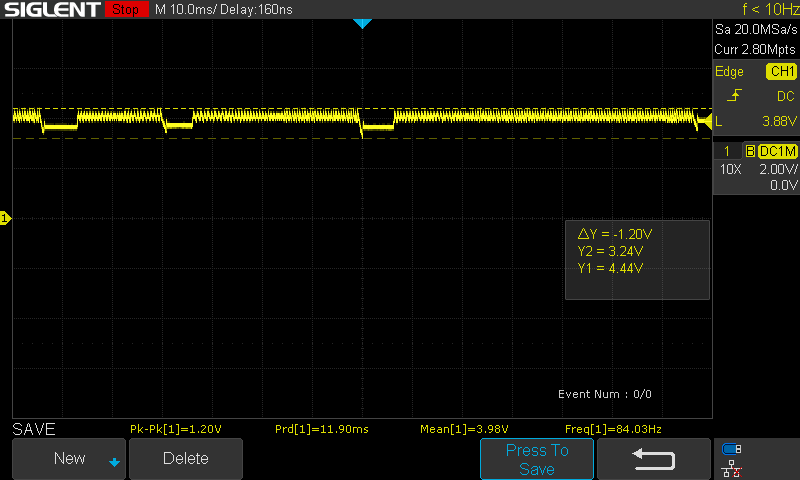

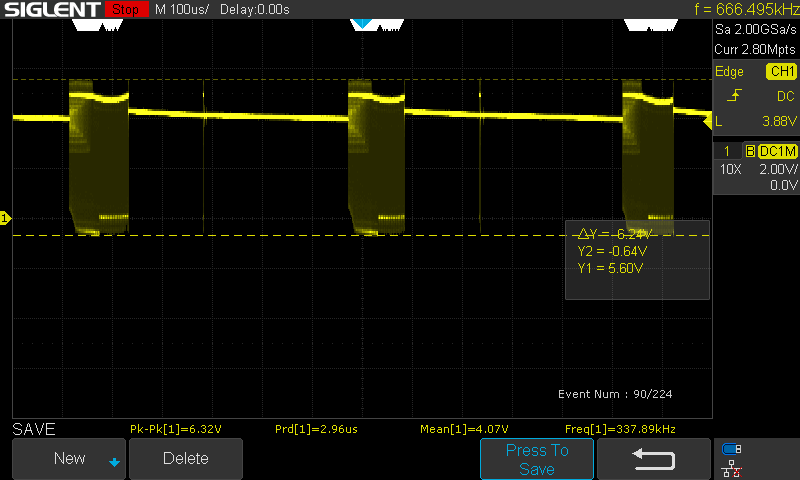

SW node: (first image overall, subsequent images zoomed parts of this trace)

Start of the pulse group

End of the pulse group

Single pulse that appears on SW