Tool/software:

This is an excerpt from the UCC28711 datasheet.

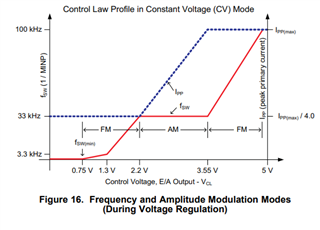

The image implies that once the average output current reaches the regulation reference, the controller transitions to frequency modulation mode to regulate the output. It also states that the voltage is maintained below the regulation target and VDD is kept stable.

Please confirm if my understanding is correct:

- The VCST (Maximum CS threshold voltage) of UCC28711 is 780mV when Vvs is 3.7, and 195mV when Vvs is 4.35.

- The Vvs regulation reference (Vvsr) is 4.05, and the controller strives to maintain this value.

- When a load is applied to the output, as described earlier, the regulation reference in the average control block is reached, and the system transitions to frequency modulation control.

- At this point, the VCST level is increasing up to 780mV according to VCST(max).

- After, the VCST value is measured at approximately 780mV regardless of the load magnitude.

- However, if the Vvs voltage exceeds 4.05, the duty cycle will be adjusted, leading to a lower observed voltage. This is because the system has already entered the frequency modulation control region, and the frequency is adjusted to regulate the duty cycle.

Is my understanding correct?

The reason I am asking this question is that in an SMPS rated at 24V/2A, I observe that the VCST value measured at the CS pin remains approximately 700mV, regardless of whether the load is 0.3A or 1.5A.

This behavior seems consistent with the datasheet's description of the controller's operation in frequency modulation mode and the relationship between VCST and Vvs. However, I would like to confirm if this is expected behavior based on the design and regulation mechanism of UCC28711.