Tool/software:

Hi,

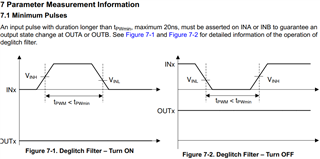

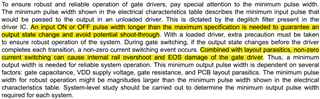

Section 8.3.4 of the November 2024 datasheet release refers to a potential risk of causing shoot-through by not adhering to a certain minimum pulse width. In addition, this minimum pulse width is dependent on many circuit parameters.

The question here is twofold:

- What are the System-level studies that should be carried out to determine the minimum output pulse width in a specific application?

- Is the shoot-through risk only because of the possible EOS driver damage during non-zero current switching events? Or is there a risk of direct shoot-through due to the output stage not changing state as indicated in section 7.1, even if there is no EOS driver damage?