Tool/software:

Hi TI Expert,

Few questions about the TPS748A-Q1 would like to check with you:

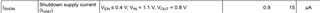

1. About the ISHDN, why we have 0.8V VOUT when VEN is lower than 0.4V, that's the leakage from VIN or we just add extra power source on OUT on purpose?

Isn't the VOUT suppose to 0V when we measure the ISHDN?

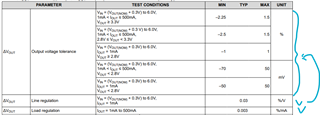

2. Since we provide both output voltage tolerance and Line/Load regulation, if we want to know the VOUT based on certain condition, will we suggest customer to use the data in "output voltage tolerance" directly?

I'm not sure whether the data we provide in "output voltage tolerance" also consider the variation of internal VREF or Offset since it's a fixed output version.

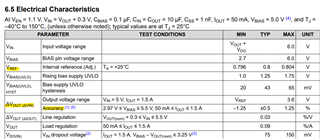

In TPS748A-Q1 datasheet(adj), we provide VREF variation but also provide the VOUT Accuracy based on BIAS pin.

So I'm confused about the relationship here.

Could you kindly share the reason that why we provide total VOUT accuracy in some datasheets but provide separate parameters in other datasheets?

Thank you.