Tool/software:

Hi, TI expert

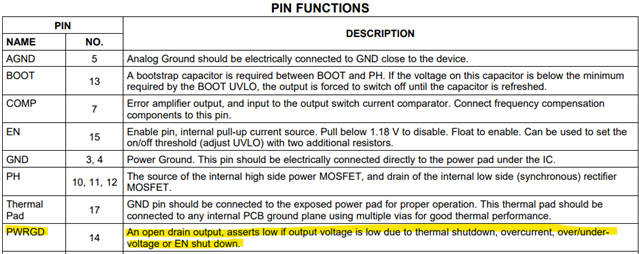

I have a customer inquiry about PWRGD pin of TPS54519RTER.

Q1) In each case of conditions that output Low: Thermal shutdown, Overcurrent, Over/Under-voltage, EN Shut down, are the Low output interval and duration the same or different?

Q2) This time, it is judged that it is not a protection condition, but it is said that there is a phenomenon in which the PWRGD pin alternates between High and Low. Is there such a case?

Is there an explanation or reference material for this?

Please check. Thank you.