Tool/software:

Hi Teams,

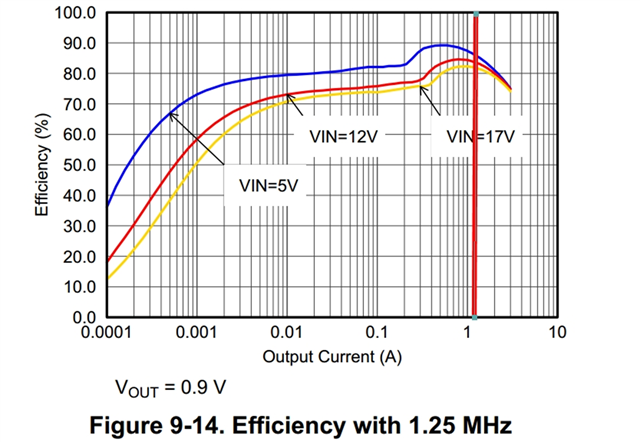

When the switching frequency is 1.25MHz, VIN=5V, Vout=1V, Iout=1.29A, The conversion efficiency of TPS62130ARGT is only about 67%, which is significantly different from the theoretical conversion efficiency given in the datasheet,

Customer testing method: Use current probes to test the current at the input and output terminals of the chip separately, and calculate the conversion efficiency;

Customer's load: This power supply is the core power supply of FPGA;

1. What testing methods does TI use when measuring conversion efficiency? Is this curve comparable to the data measured in the customer's application scenario?

2. What are some suggestions to improve conversion efficiency for customer application scenarios?