Other Parts Discussed in Thread: LM70860, LM70660, LM5148, CSD19532KTT, CSD19532Q5B

Tool/software:

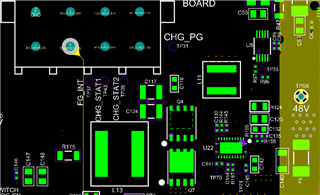

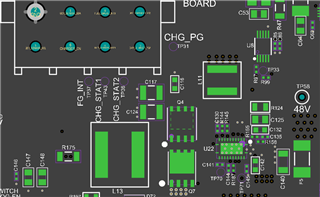

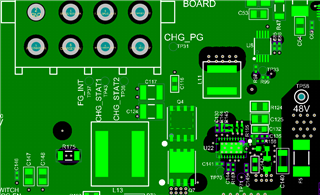

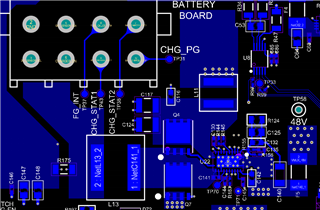

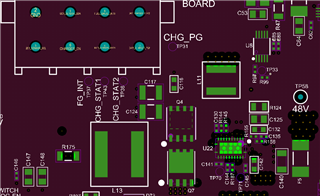

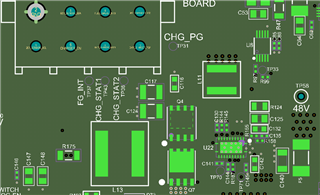

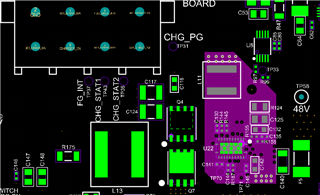

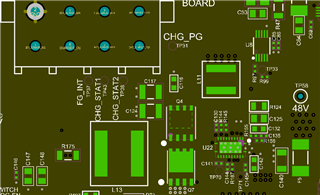

I am currently debugging a LM5149 design for a high power industrial application. I am trying to troubleshoot an issue with the output voltage dropping out of regulation at lower than expected output currents. We expect to achieve 4A, when the output drops by several volts at around 1A of output current. As I debug the issue, I would like to force the regulator to run in continuous switching mode to compare the performance. However, when I ground pin 18 as noted in the datasheet, the regulator instead outputs zero volts, and probing the SW node reveals that the regulator is not switching at all. I have verified that the enable pin is still being pulled up to the input voltage. What could be causing this?