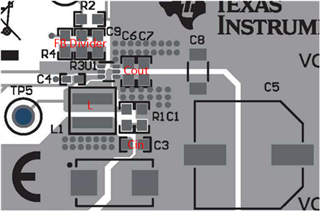

Other Parts Discussed in Thread: TPS61099EVM-023

Tool/software:

Hello Travis,

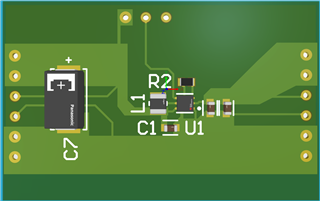

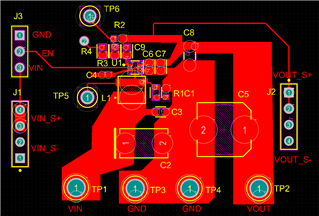

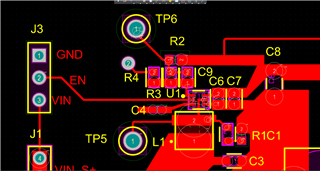

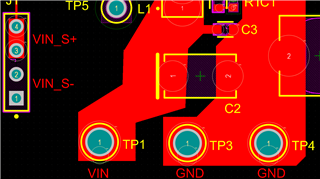

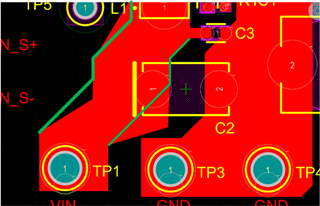

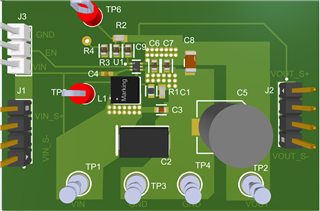

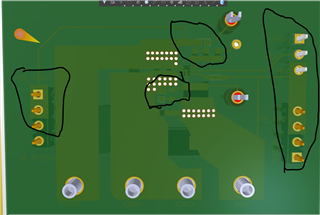

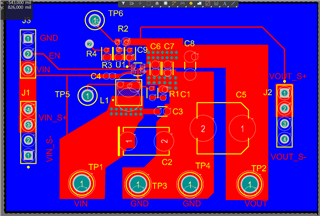

As you mentioned, I have made the adjustments. Since I use a MacBook Air M1, I cannot use Altium; instead, I am using the EasyEDA Pro Desktop software. I researched and implemented the adjustments as per your suggestions. I cannot thank you enough for your support.

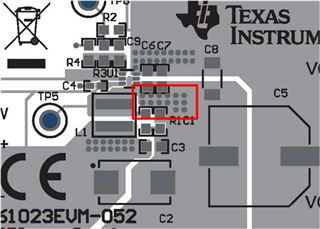

and one note ı draw it later -052 when you accept this desing.