Tool/software:

Hello,

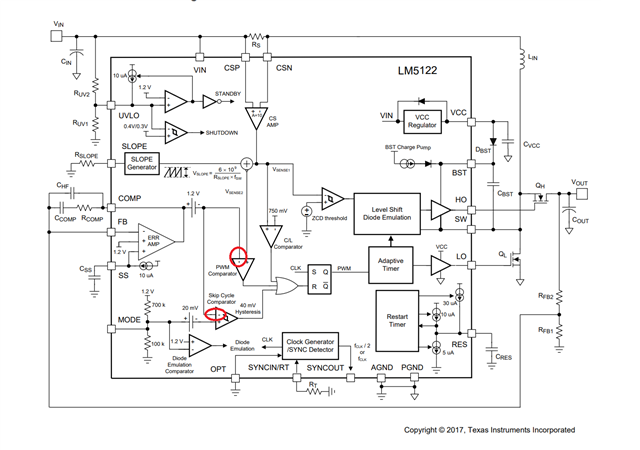

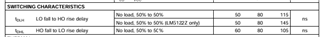

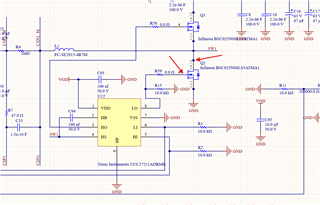

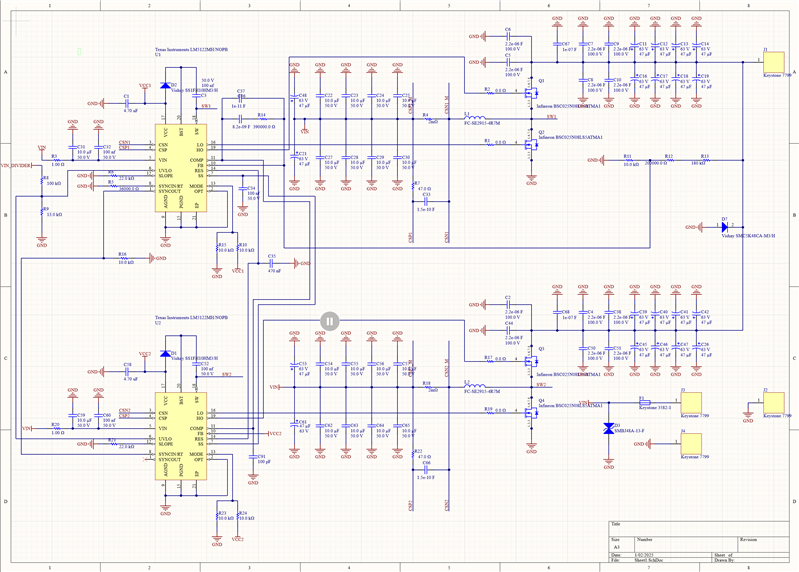

I am working on a 300W 12V to 48V boost converter, this is based on a 2phase boost converter based on the LM5122.

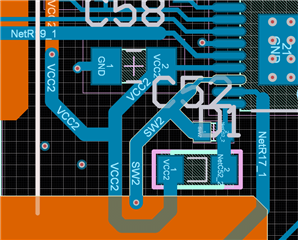

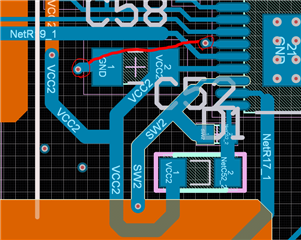

The schematic is shown below:

When only the master is stuffed, the converter starts properly.

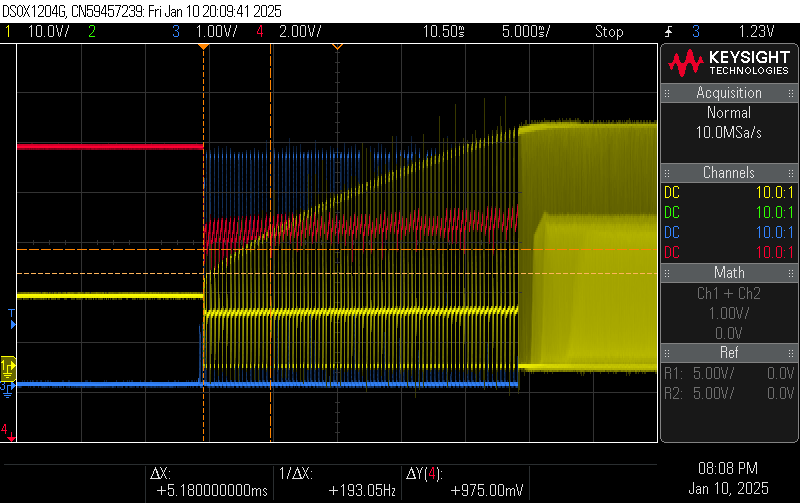

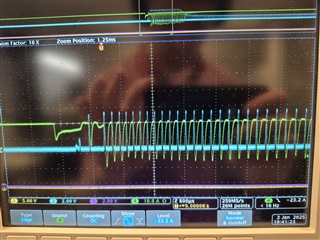

However when the extra slave converter is added, there is a strange behavior visible.

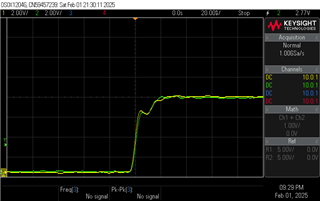

During startup of the converter or with a load, when the converter(s) start switching the output of the error amplifier starts rising very quickly ~1V/50us and commands a very high current from the inner current loop.

This results in a large voltage drop at the input, this voltage drop triggers the UVLO of the converter and is disabled and start up again.

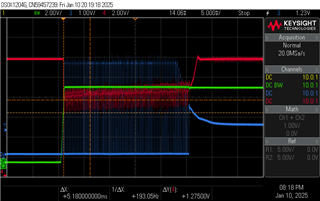

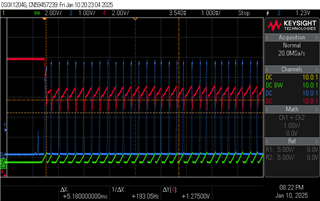

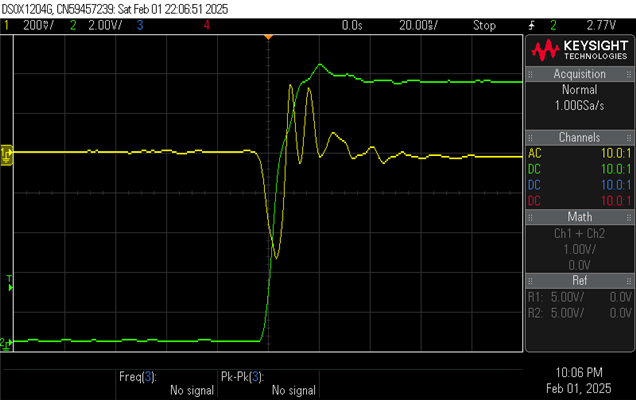

This is shown in the scope plot below, green is the input current and blue is the output of the error amplifier.

Normally such a steep response isn`t expected because the bandwidth of the error amplifier is quite slow, the slave error amplifier should be disabled because the FB is connected to VCC (output of internal LDO)

So i don`t see any situation where this behavior is possible.

I double checked the schematic a couple of times but i can`t see where there could be a problem, i also tried different operation modes but the problem stays the same.

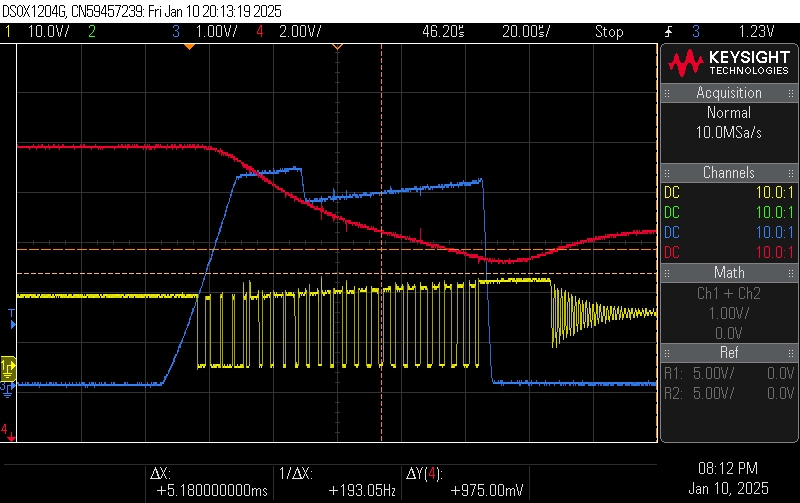

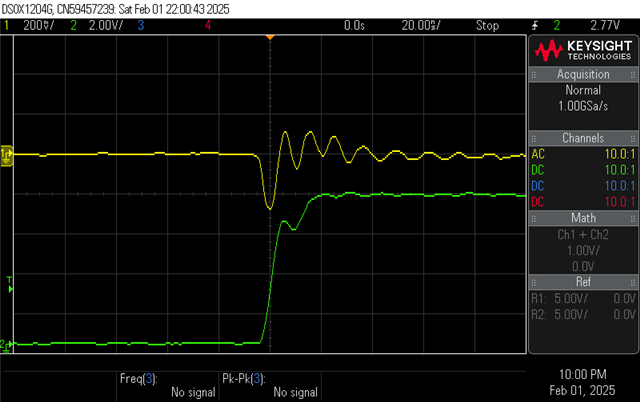

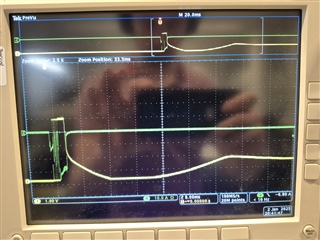

After doing some double checking and removing the slave controller, the problem is also visible with just the master controller.

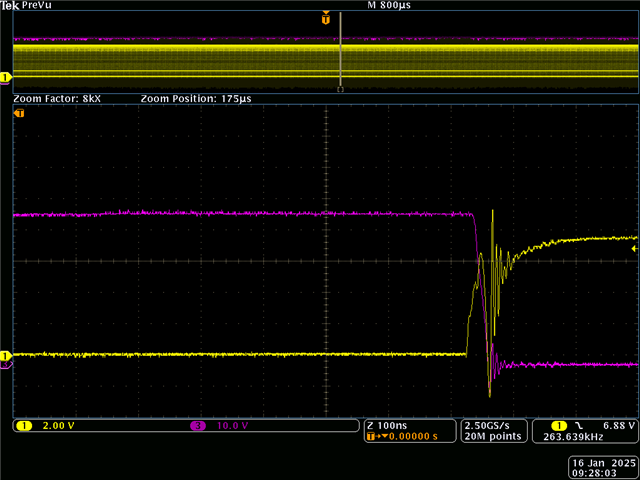

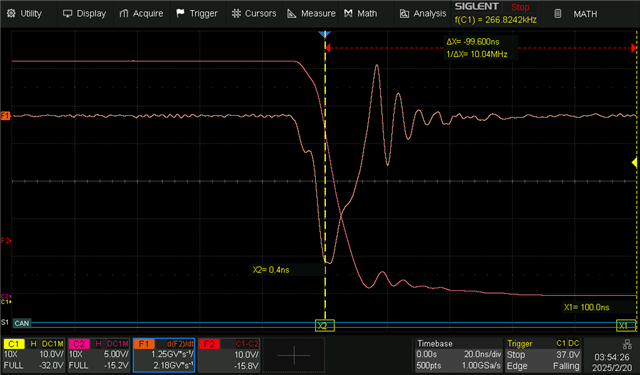

During startup there also unexpected transients visible on the ouput of the error amplifier (Yellow trace)

Kind Regards

Alexander

Kind Regards

Alexander