Tool/software:

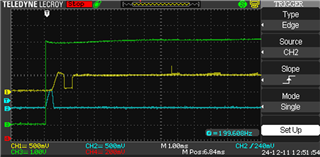

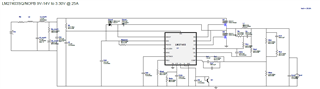

We have a design where the design never switches on startup. A 33nF capacitor is connected to SS but as can be seen below, SS never starts to rise as would be expected. VDD is present as expected. The only difference to the schematics shown below is that the UVLO/EN is driven by the PG of another regulator. Must it be driven by VIN or can VIN be present prior to UVLO/EN? Any suggestion as to what might cause this behaviour. We have tried connecting OTP to GND and we also connected D+ to D- to GND but neither of these changes made any difference to the behavior shown below.

CH1: COMP CH2: SS CH3:UVLO/EN