Other Parts Discussed in Thread: LM74800-Q1, LM74700-Q1

Tool/software:

Hello

The part within the LM7480-Q1 family is the M74800-Q1.

The requirement for a design is an ideal diode on a charger input to a battery. We only need to protect the battery from reverse current back through the charger input so surge and overvoltage protection are an added feature on the M74800-Q1. The CVCC charger provides some regulation of start currents so inrush isn't an issue from out tests.

The design also senses the charger input voltage at an MCU and the circuit has the resistor divider at the M74800-Q1 EN pin to disable the FETs at undervoltage.

The issue to consider is when the charger input is disconnected during charging; that is, typical removal of the charge plug while active.

Datasheet section 9.3.2.1 Reverse Battery Protection (A, C, DGATE) describes:

In LM74800-Q1 the voltage drop across the MOSFET is continuously monitored between the A and C pins, and

the DGATE to A voltage is adjusted as needed to regulate the forward voltage drop at 10.5 mV (typ). This closed

loop regulation scheme enables graceful turn off of the MOSFET during a reverse current event and ensures

zero DC reverse current flow. This scheme ensures robust performance during slow input voltage ramp down

tests. Along with the linear regulation amplifier scheme, the LM74800-Q1 also integrates a fast reverse voltage

comparator. When the voltage drop across A and C reaches V(AC_REV) threshold then the DGATE goes low

within 0.5-μs (typ). This fast reverse voltage comparator scheme ensures robust performance during fast input

voltage ramp down tests such as input micro-shorts. The external MOSFET is turned ON back when the voltage

across A and C hits V(AC_FWD) threshold within 2.8 μs (typ).

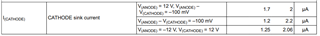

If the input disconnects and floats this won't have reverse current. I can put a high value resistor from charge input to ground but I need to understand the minimum reverse current that will turn the FETs off and allow the charge input to decay to an undervoltage condition. That way the undervoltage will disable the M74800-Q1 charge pump and go to shutdown and the MCU can also sense removal of the charger.

I apologise if the datasheet has this threshold and I missed it.

The related question is if the LM74700-Q1 has a similar regulation as above. If so, what input pull-down resistor minimum reverse current is required ? If I can use the LM74700-Q1 it is smaller, cheaper, and requires less support parts as well as meeting the requirements.

All the best

Harry