Tool/software:

Hi,

I use the TPS56C231 as 0V85 driver on a PCB with other Voltage supplies. I have following Power Sequencing: ... ->5V_REG -> 0V85 -> 0V9 -> ...

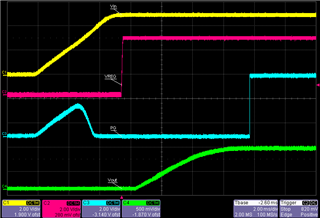

The 0V9 supply is activated with the PG signal of the TPS56C231 (PG_0V85)

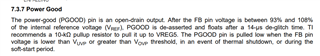

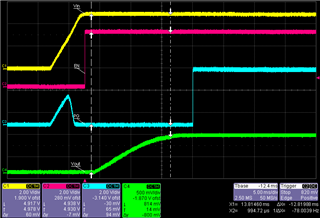

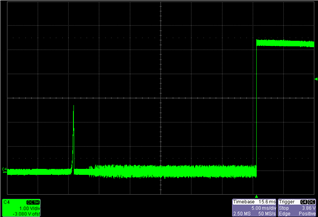

Measurements show that there is a short pulse of PG_0V85 before 0V85 is on:

This causes to enable 0V9 for a short time which is problematic.

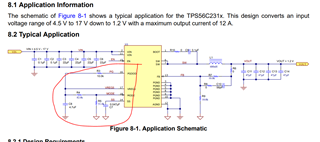

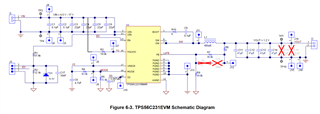

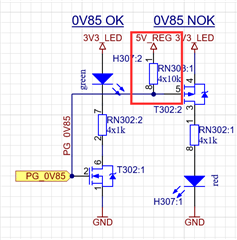

PG_0V85 is pulled high with 10k to 5VREG:

Other to this Pullup and the connection to 0V9 Driver Input, PG0V85 is not connected anywhere else.

I could reproduce this behavior with the Eval-Board TPS56C231EVM.

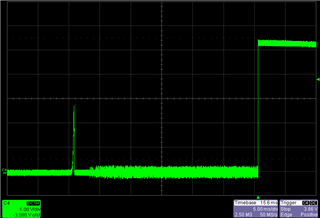

There I connected PG via 10k to Vin.

This shows a small Pulse on PG which should not be.

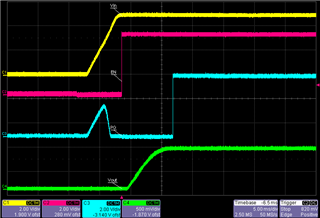

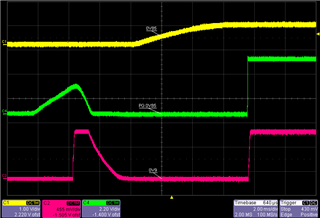

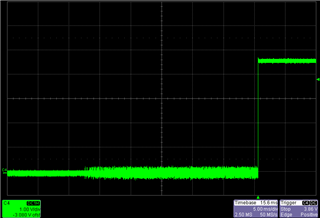

With the original circuit in which PG is pulled high to internal TPS56C231EVM voltage VREG5, this pulse does not occur:

My resumée:

- Power Good output pulled to Voltage which is on before TPS56C231 enabled -> faulty short pulse on PG signal

- Power Good output pulled to internal TPS56C231 VREG5 -> expected behavior without pulse

Is this a known issue? Or am I the only one who can observe this pulse? Is PG output undefined for some time during startup? Is it mandatory to connect PG to VREG5?

Thank you a lot