Other Parts Discussed in Thread: UCC21551, UCC25800

Tool/software:

Hi,

am planning to use ucc21551-q1 as my dual isolated gate driver for the SiC (SCT018H65G3AG) based PSFB , suggest me how to configure this driver to get +18 at high side and -3 at low side with 200khz frequency operation, if any other better part available let me know it as well

thanks and regards

Swathin

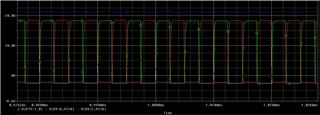

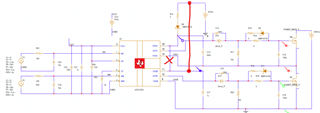

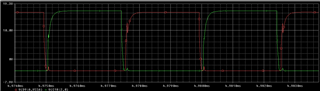

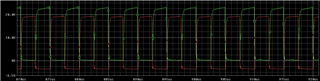

. when I replace the top mosfet with a capacitor (gate to source with same Ciss 2124p) this is working normal.

. when I replace the top mosfet with a capacitor (gate to source with same Ciss 2124p) this is working normal.

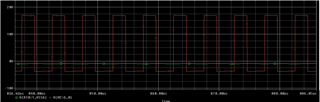

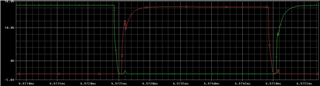

What is causing the VDDA to fall to zero volt when switching.

What is causing the VDDA to fall to zero volt when switching.

how to resolve this.

how to resolve this.

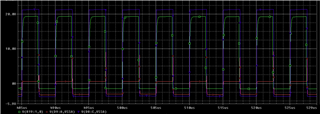

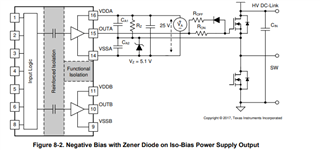

How to select the capacitor values for CA1 and CA2? in this configuration

How to select the capacitor values for CA1 and CA2? in this configuration

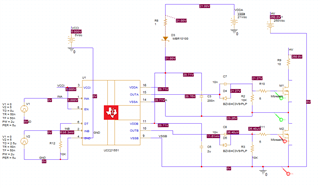

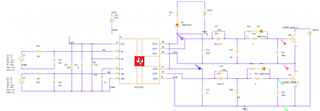

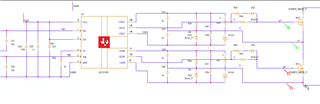

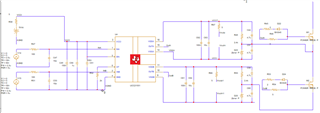

this is the schematic i made for the application but

this is the schematic i made for the application but power mos p parameters are edited as per real switch bias voltage is coming from ucc25800 based power supply

power mos p parameters are edited as per real switch bias voltage is coming from ucc25800 based power supply