Tool/software:

Hello mike,

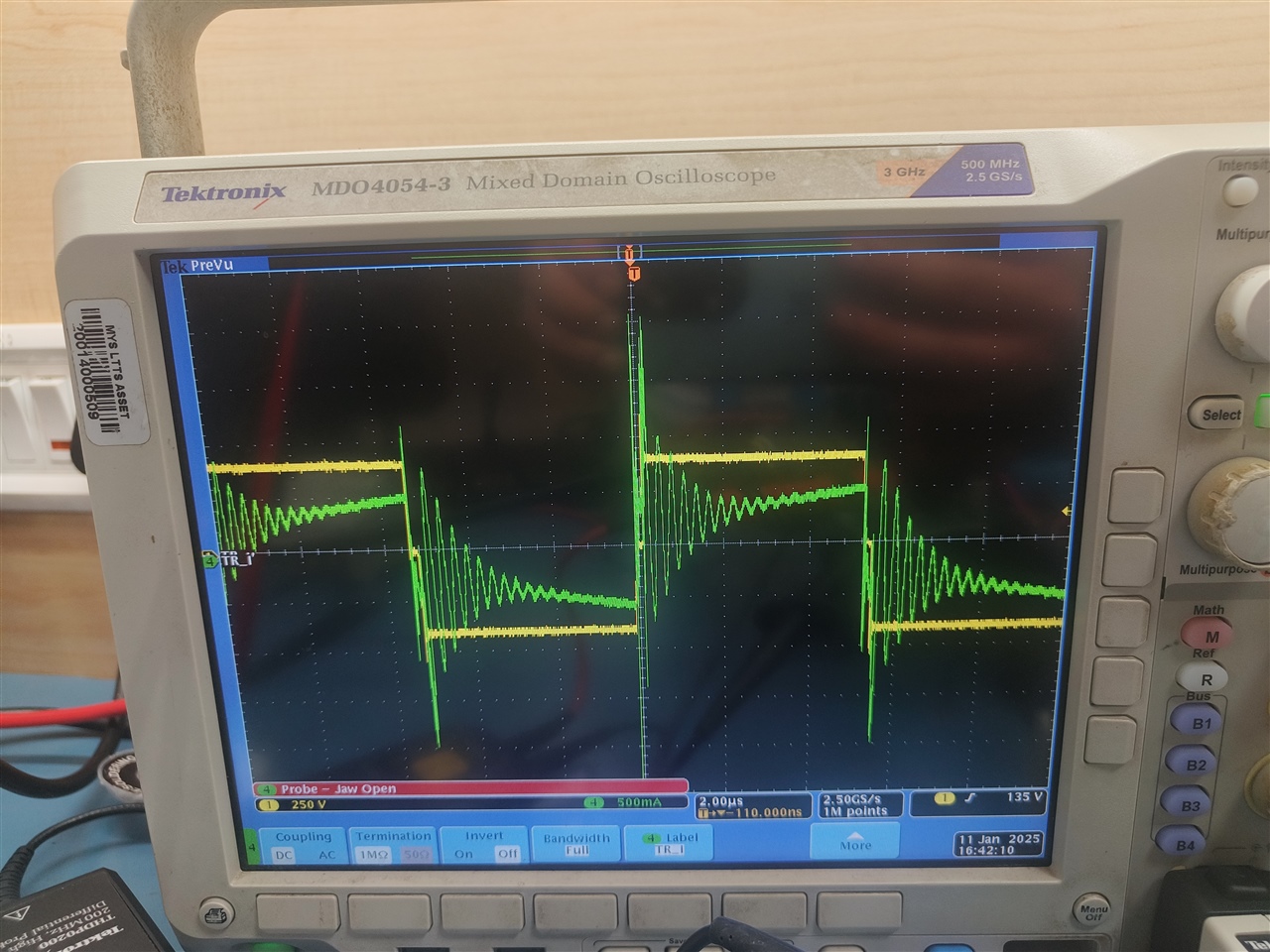

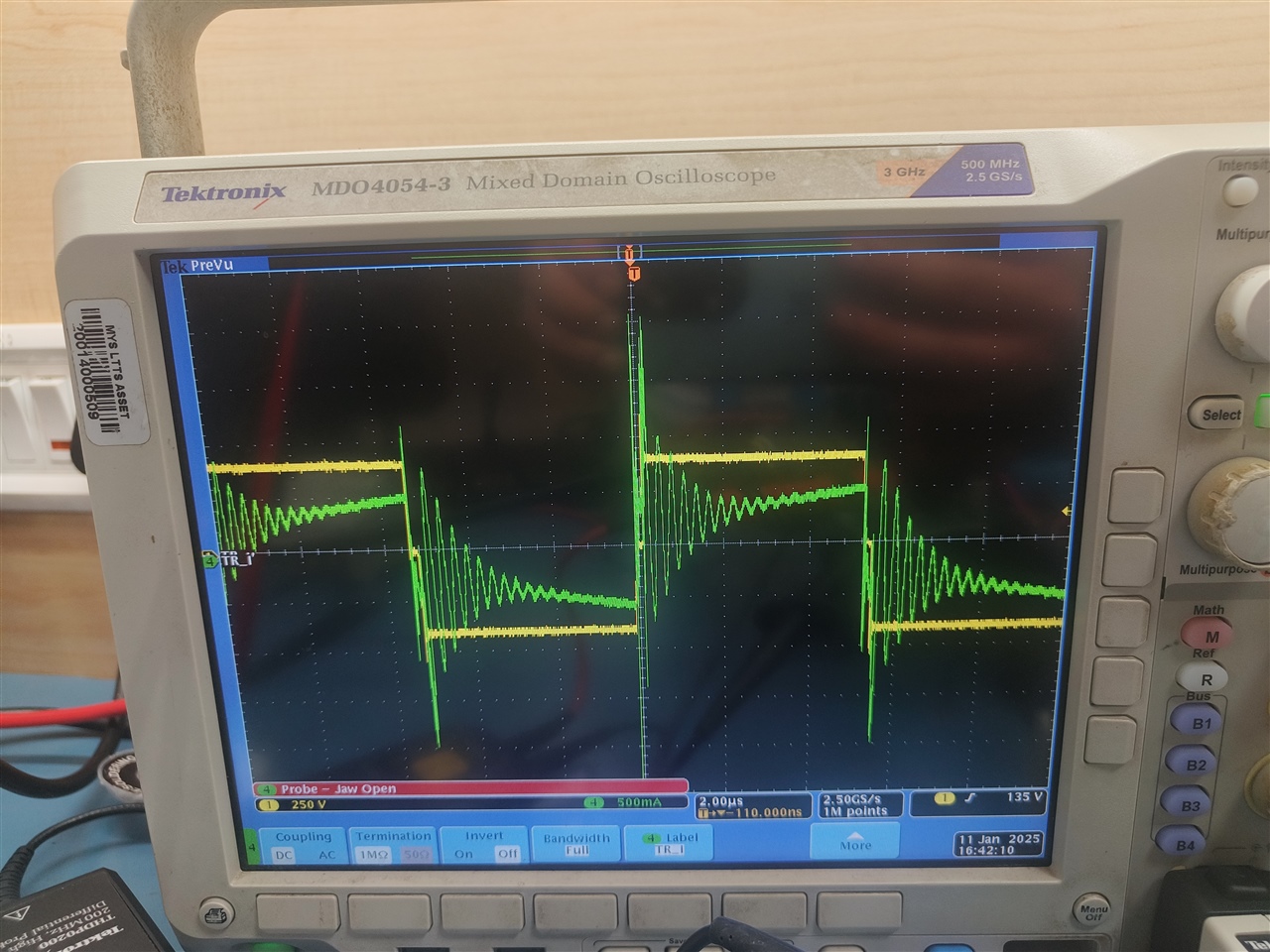

I have oscillations in transformer primary current waveform. Not seen in my earlier designs. Transformer primary voltage looks Ok.

Below is the waveform.

Output there is no RCD Clamp or RC snubber as of now.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hello mike,

I have oscillations in transformer primary current waveform. Not seen in my earlier designs. Transformer primary voltage looks Ok.

Below is the waveform.

Output there is no RCD Clamp or RC snubber as of now.

Hello,

C and Ls will oscillate when exited by electronic stimulas. I remeber that you were expierementing with moving the bulk capacitor away from the H bridge.

If you did this it would have increased the trace inductance between the H Bridge and the bulk. This added inductance can cause additional ringing. It is roughly 10 nH/in or 10 nH/2.54 cm.

Did you move the bulk capacitor away from the H Bridge? If you did I would recommend moving it closer to the H Bridge.

Regards,

Hello Mike,

Bulk capacitor issue is not present. It seems to work with that change.

Oscillations what I have observed is w.r.t to output ( synchronous rectification) MOSFET coss. I have added more mosfets with lesser RDSON for better efficiency purposes. In comparison to previous version of board, it was almost 10 times more.

Previous FETs ( 2 in parallel) : 196pF

New board new FETs ( 4 in parallel) : 1.2nF

I tried removing all , keeping only one FET for each winding. It works with much reduced oscillations. There are still some, I think we can add RCD CLAMP and RC to reduce it. Can you please explain is this resonance of some kind. Please give some detailed information for better understanding

Hello,

In power supply design dealing with L and C rining is common. If you change C or L with circuity changes the ring signature will changed. If you change your layout this will change your parasitic Ls and Cs; as well, and change your ring signature also.

The Q factor is generally tied into your ringing amplitude and durration. The higher the Q the more ringing you will have in your design. The lower the Q the less ringing you will have in your desing. If you have a Q factor of 1 generally the ringing is critically damped.

Q = (1/R)*(L/C)^1/2

Changing the FET total capacitance will affect ringing that you see. So it is not surprising changing the amount of FETs being used will change the ring signature.

An RCD clamp on the secondary SRs will also discharge some of the ring energy as well to reduce ringing. You could also add a snubber across the SRs as well to reduce ringing.

In regards to setting up a snubber the following application note may be helpful. It is actually written for flyback converters; however, there is a good section on how to setup an RC snubber across the output rectifier. This technique used will work for the SRs in your application.

https://www.ti.com/lit/an/sluaac5/sluaac5.pdf

Regards,

Hello mike, the I tried adding RCD Clamp, it's effective. But resistor is heating severely. And sometimes diode gets damaged.

Diode rated for 300V

Resistor: 1kohms

Capacitor: 0.1uF

Hello,

Your R might be too large in your RCD clamp. Your diode and R need to be sized to supress the leakage energy (E) form your leakage inductance (Llk).

E = (1/2)*Llk*I^2

P = E*(ring frequency)

Your resistor needs to be sized correctly for the correct power (P).

P = I^2*R

Your diode needs to be sized correctly to handle the power (Pd) as well.

Pd = Id*Vd

Sizing the components for a greater power rating than required will drastically reduce component heating. I would recommend a factor of 2 or greater.

I found this thread that you might find helpful as well to setup and RCD clamp for a PSFB.

Regards,