Other Parts Discussed in Thread: TPS65994BH

Tool/software:

Dear TI

For Intel re-time FW capsule update in BIOS, I encounter a FW update problem.

My environment:

CPU: Intel Meteor Lake

OS: WIN11 24H2

Retimer FW: HBR_MTLARL_MPS_A0_6.23.1V3_Rel_ALL_Prod_PV1_External_SEC1_sign.bin

Attempt to update to: HBR_MTLARL_ALL_ALL_6.24.2V2_Rel_ALL_SEC1_PROD_external_sign.bin

1. With F909.12.06 base, I can do re-timer capsule update successfully (After install driver, WIN11 reboot, and BIOS can update the re-timer FW, progress bar in BIOS finished in 60s)

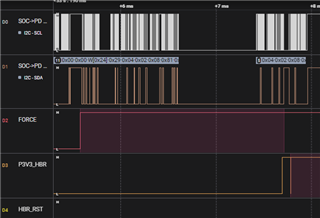

2. With F909.12.30 base, I can NOT do re-timer capsule update successfully (After install driver, WIN11 reboot, and BIOS can update the re-timer FW, progress bar in BIOS finished in 7s)

3. I narrow down the issue: the WIN11 device manager > Device Firmware > Firmware version

In F909.12.06 base, Device Firmware Version can show the firmware version as 26F (which is 623)

In F909.12.30 base, Device Firmware Version always show 0

4. Here is the step I force the BIOS to fetch the firmware version: In UEFI shell, delete the variable TbtRetimer1Version

5. Do I need to send the pjt file to you, if so, where to send ?