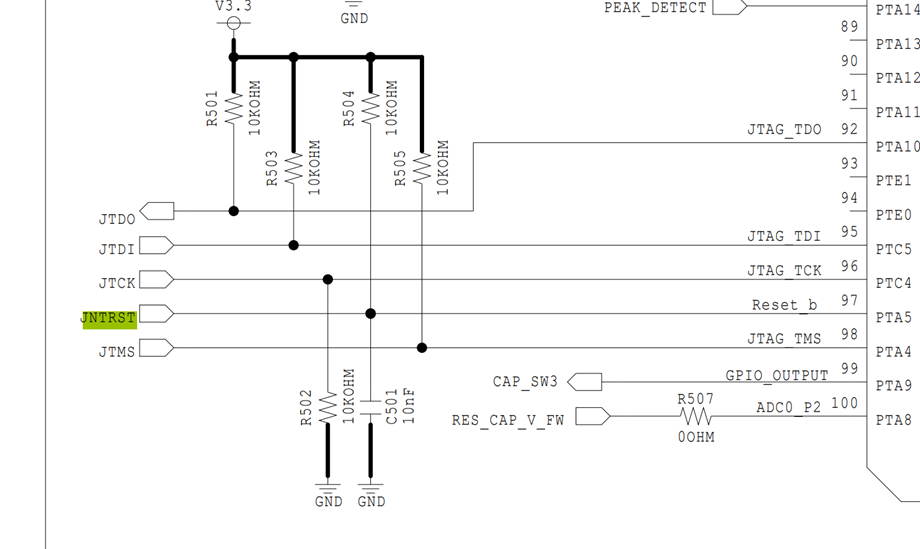

Tool/software:

Dear TI experts,

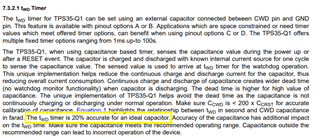

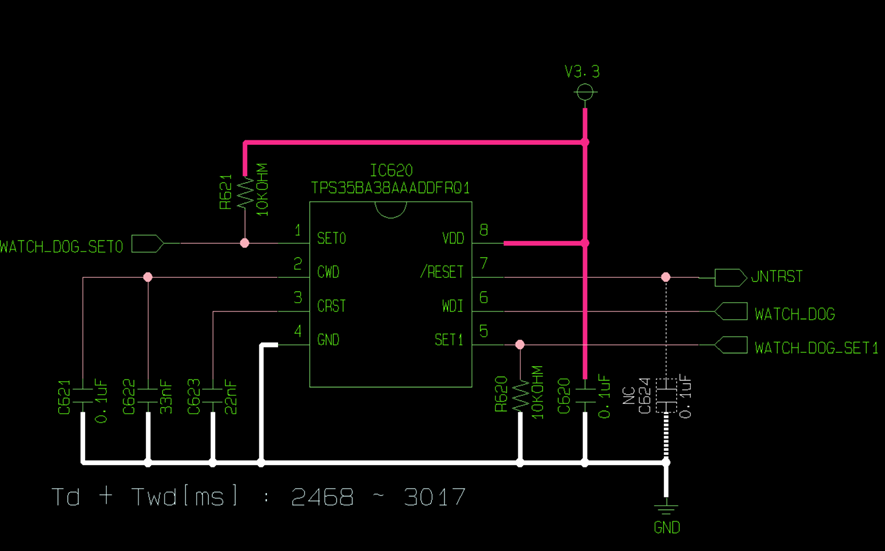

My customer draw their first schematic using TPS35BA38AAADDDFRQ1. Could you review this schematic?

My customer wants to make a watchdog about every 3 seconds. So My customer calculated tD and tWD as follows.

: Reset time delay = tD (sec) = 4.95 × 10^6 × CCRST (F) = 4.95 × 10^6 × 22nF = 108.9ms

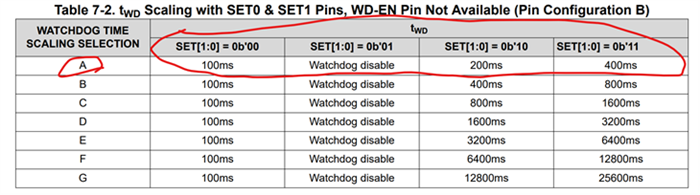

: Watchdog timeout period = tWD (sec) = 4.95 × 10^6 × Ccwd (F) = 4.95 × 10^6 × 133nF = 658.35ms -> mutiply 4 for time scaling -> 658.35ms X 4 = 2633.4ms

=> 108.9ms + 2633.4ms = 2742.3ms => about 3 seconds of watchdog time made regarding 10% maximum error rate.

Here are my additional questions ;

1. Please review the schematic especially the passive components.

2. Is my calculation for watchdog time right? or could you suggest other way?

3. How can I set SET[1:0] for midfix "A" device? is the below table is right? -> So I can set SET[1:0] pin both 1 for x4 scaling.

4. What is difference between tWD(Watchdog timeout period) and tWDO(Watchdog timeout delay)? Is it right to use tWD for calculating watchdog time?

5. How can I estimate maximum and minimum error rate (also accuracy) for watchdog time? Is 10% normal value for accuracy?

Please check these issues. Thanks.

Best regards,

Chase