Other Parts Discussed in Thread: DRA821

Tool/software:

Dear Team,

My customer is evaluating the TPS6594-Q1 for powering to DRA821. They use nRST_OUT output of the TPS6594-Q1 for PORz signal of the DRA821.

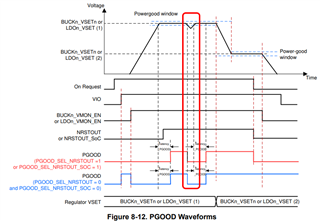

This nRSTOUT monitors BUCKn_VSETn or LDOn_VSET, and goes low if the BUCKn_VSETn or LDOn_VSET fall out of the Power-good Window range.

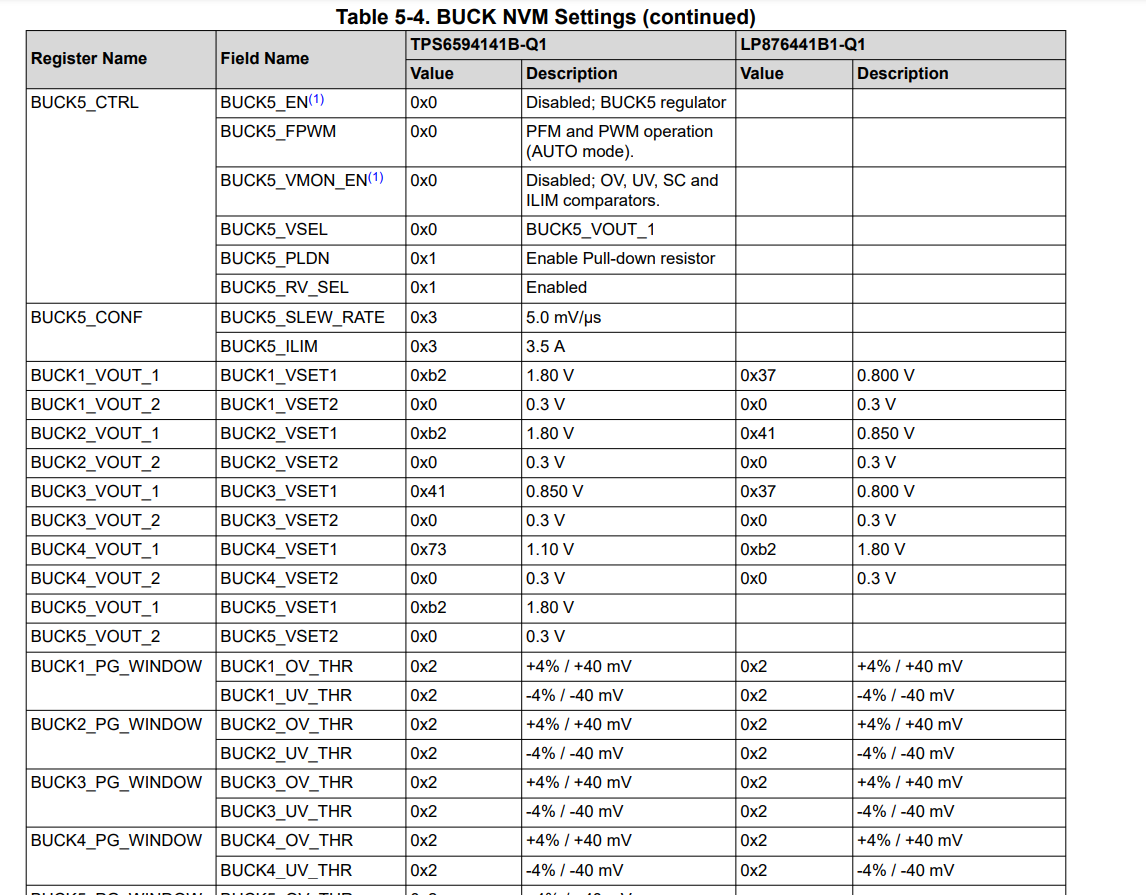

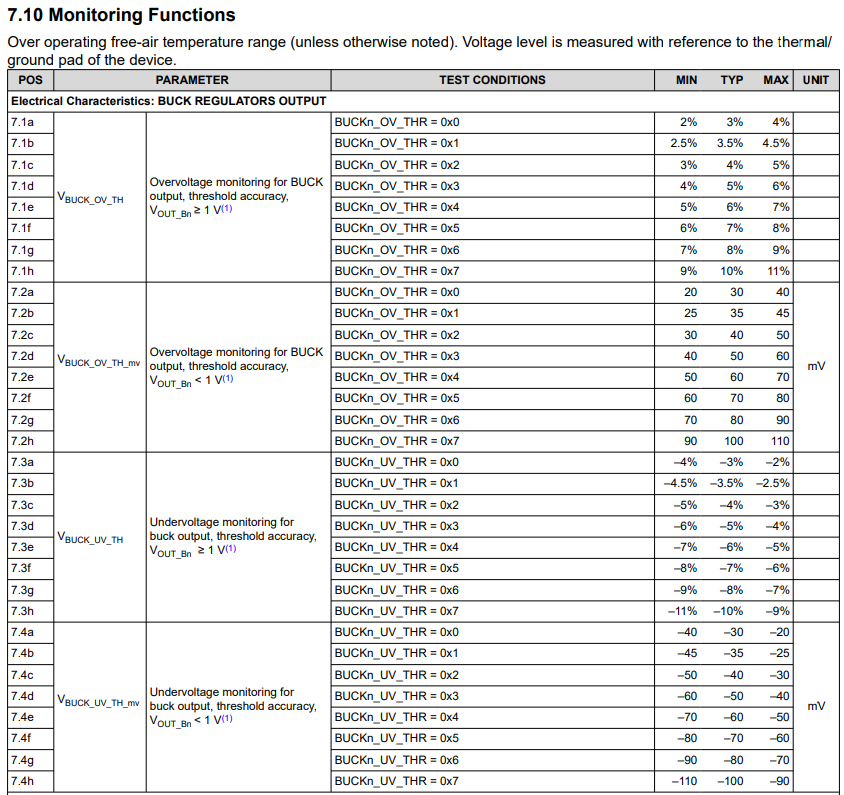

Can you let us know the default value of this Power-good Window, default value of the BUCKn_VSETn and the LDOn_VSET, please?

Best Regards,

Koshi Ninomiya