Other Parts Discussed in Thread: DRA829J-Q1, DRA829

Tool/software:

Hello,

I use a DRA829J-Q1 supplied with two PMIC according PDN-0C on my HW.

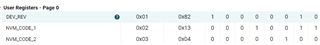

Measurement of the To_standby Power Sequence compared to SLVUC99A Figure 6-3 show deviation on two supply rails:

TPS65941213-Q1 LDO4 starts switching of at 3090µs after beginning of sequence, expectation would be 500µs.

![]()

CH1: TPS65941213-Q1 Enable Pin

CH2: TPS65941213-Q1 LDO4

CH3: TPS65941111-Q1 QPIO3 (EN_VDDR)

CH4: VDDR

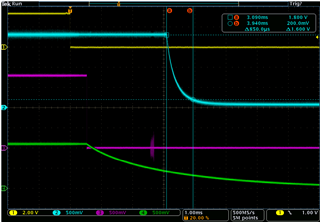

PS65941213-Q1 BUCK4 starts switching of at 536µs after beginning of sequence, expectation would be 2500µs.

CH1: TPS65941213-Q1 Enable Pin

CH2: TPS65941213-Q1 BUCK1:3

CH3: TPS65941213-Q1 BUCK4

CH4: TPS65941111-Q1 BUCK1:4

Is this a known behaviour and will be corrected in PDN-0C, or is there somthing wrong in my circuit?

Regards, Peter