Other Parts Discussed in Thread: UCC14240-Q1

Tool/software:

Dear Ti,

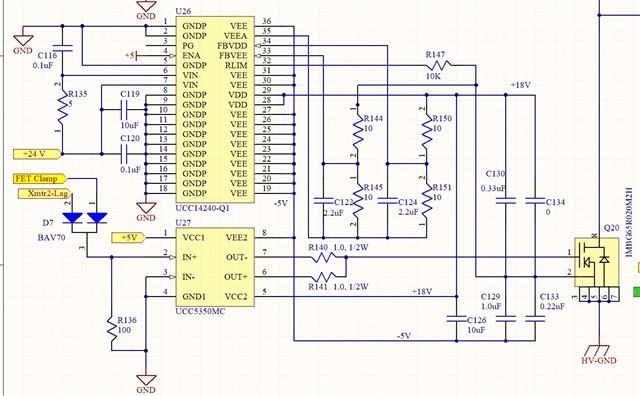

Attached is a layout for a SiC FET driven by the isolated driver and supply: UCC5350MC and UCC14240.

Questions: I eliminated the ground plane under the driving pins, but still have a big trace for the FET Gate Common lead to connect all the capacitors. How wide can this be, or will it create parasitic capacitance under the Gate leads.

Shall I include the Miller Clamp resistor R140, just in case, or is there no possibility for it and eliminate it?

There are still long traces for the capacitors. Is this acceptable?

I look forward to your experienced review.

Thanks.