Tool/software:

Hi,

while working with the SOA calculation sheet some questions emeregedwhich hopefully you can answer me:

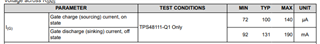

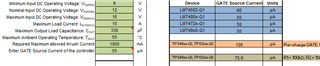

- Where does the recommended value for the "gate source current" (75,6uA in case of the TPS4811) come from?

- How does it change when varying the gate resistor R1 (~100k) and what is it dependedn from?

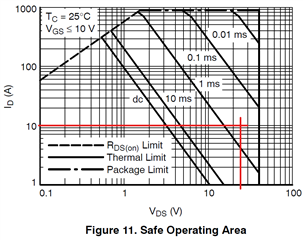

- What should i enter in, for example, F55 (1ms SOA Current @ VIN(MAX)) if the voltage is already outside the SOA? It doesn't let me enter 0A, so i resided to 0.0..01, which worked fine

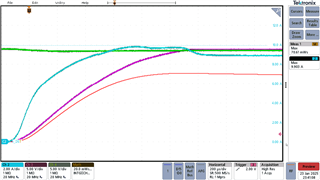

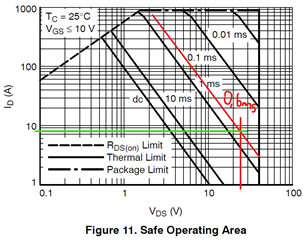

- How do I work with the SOA graphic of the MOSFET if neither the current through nor the voltage over the MOSFET are linear/constant?

If read the application note SLUOOA2 regarding the SOA but it wassn't really applicable in my case, at least I didn't see how.

Can I just integrate the power of the FET during turn-on over time and find an approximation using a square wave with the same energy integral?

I can't imagine this a good starting point, because since, at least simplified, E = U x I x t gives me 3 variables to play around, I can achieve many very different operating points while keeping the energy constant.

Or do I use the worst case V_DS and I_DS over time (like in the application note) and adjust just the time to achieve a pulse with equivalente energy?

I will add an oscilloscope measurement afterwards.

Currently, I'm using a NTMFS5C410N from onsemi as MOSFET in a 24V system.

Probably I will switch over to a FET with 60V/80V V_DS to have a higher margin.