Other Parts Discussed in Thread: TPS2557, TPS2559

Tool/software:

Hi,

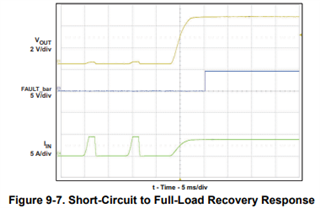

We are configuring "AutoRetry" circuit on TPS2556 by refering section "10.2.1.2.3 Auto-Retry Functionality" of datasheet.

However, We now do NOT implement "Cretry" capacitance.

According to above section, this capacitance is used to control "auto-retry" time, however, I would like you to confirm whether it is OK that we do not implement this capacitance or not.

Our concern is whether oscillation will be happened when we control "auto-retry" time too fast.

Could you please confirm about above cirucuit and give me comment if any concern exist ?

Best Regards,