Tool/software:

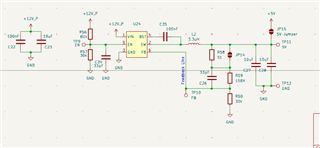

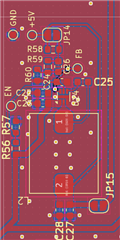

I designed some buck converters for my pcb, trying to follow the design guidelines specified in the datasheet and the values suggested. When testing the response to a transient consumption and ripple current I get pretty high values. What could cause this issue? Is it mainly a layout issue or more related to component selection?