Other Parts Discussed in Thread: LM5023

Tool/software:

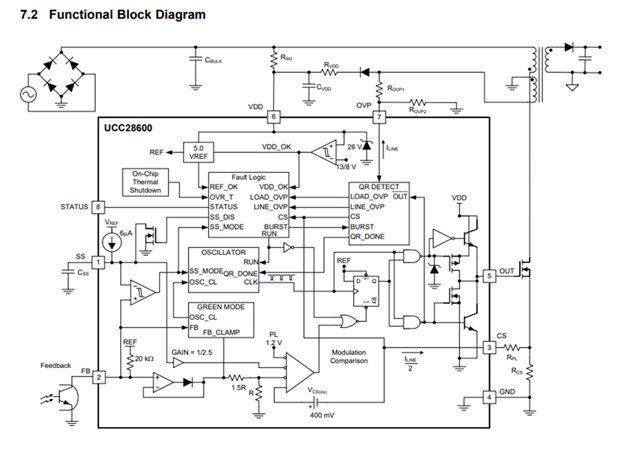

Thank you for the useful article from previous thread, SLUAAC5, that you shared! It provided great insights into the fault detection mechanisms, and I tried probing the CS and OVP pins as suggested. After making some updates to the schematic, based on reviewing the datasheet, I found that there is no longer an issue with the OVP pins.

However, I'm still facing some challenges with the Rcs and Rpl values. There seem to be multiple formulas for calculating them in the datasheet, and the design calculator uses a different approach. Could you kindly guide me on which method is more accurate or how to approach these calculations more effectively?

I’ve also attached waveforms for different input voltages. The converter now behaves as expected at both 120 VDC and 180 VDC inputs, but the primary current shape still doesn't appear as a smooth ramp. At a 250 VDC input, the output doesn't go above 5 volts, even though the primary current continues to increase when it should decrease. At 325 VDC, as shown in the attached waveform, it seems the OVP is not triggering, which could be related to the problem.

Could you provide further suggestions on resolving this issue? Also, if possible, could you recommend a flyback controllers that includes Output OVP functionality and can operate above 200kHz?

also I want to mention that the LM5023 was mentioned in previous post because the SPICE models I used are proven to be reliable, so I don’t think the issue is model-related.

Updated Schematic:https://workdrive.zohopublic.in/file/m492ucd8cc3e83a364cc6b0a90e9bdbc400df

Waveform at 120VDC input:https://workdrive.zohopublic.in/file/m492u5ff8c6947f4b4f50a412d70b7a5273d0

Waveform at 180VDC input:https://workdrive.zohopublic.in/file/m492uaa947a8f9e7844bfb0349eaa147a3f61

Waveform at 250VDC input:https://workdrive.zohopublic.in/file/m492u9774f21ad54041df8cc8c9ecc745ec0a

Waveform at 325VDC input:https://workdrive.zohopublic.in/file/m492uf86440051c0840ed9f9f13935836fcb3

Looking forward to your suggestions!

Regards,