Other Parts Discussed in Thread: UCC5350, UCC5310,

Tool/software:

I hope you are doing well.

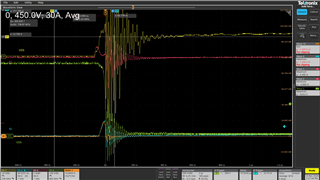

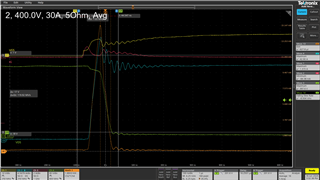

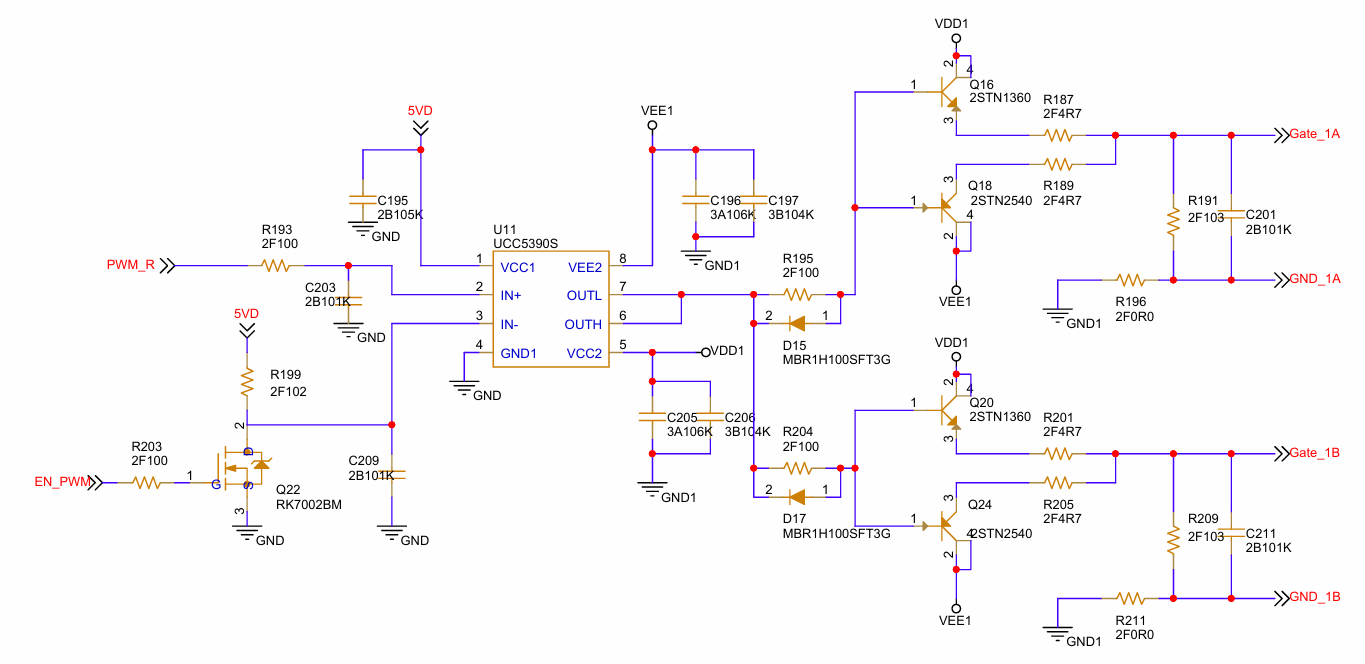

I have designed an FET drive circuit using the UCC5390S, but I am currently experiencing significant FET ringing and am seeking a solution.

- I am considering removing the push-pull circuit. Could you kindly confirm whether the UCC5390S is capable of driving two FETs? The datasheet indicates a sink current of 10A.

- I believe that using the UCC5350M Miller Clamp IC could help mitigate this issue. However, would I need to use one IC per FET?

- If you have any additional recommendations for resolving this issue, I would greatly appreciate your advice.

Thank you in advance for your support.

Best regards,