Tool/software:

Hello to all.

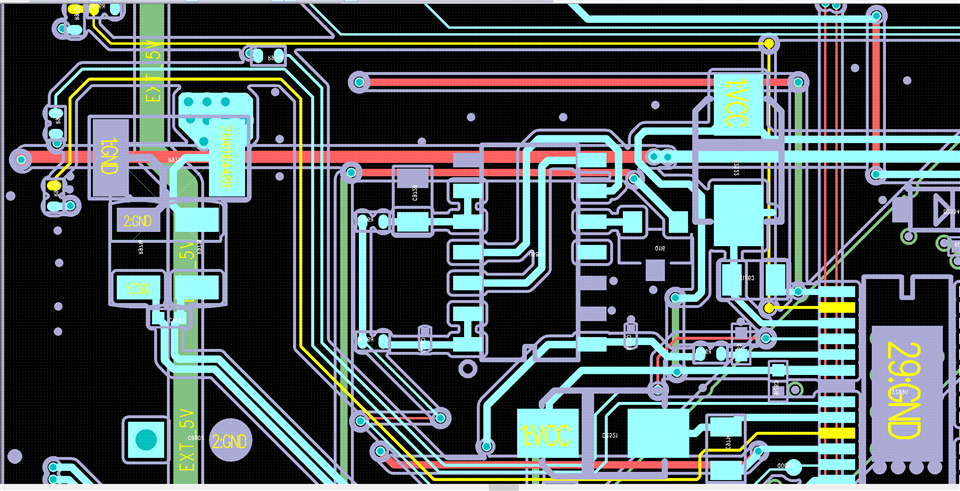

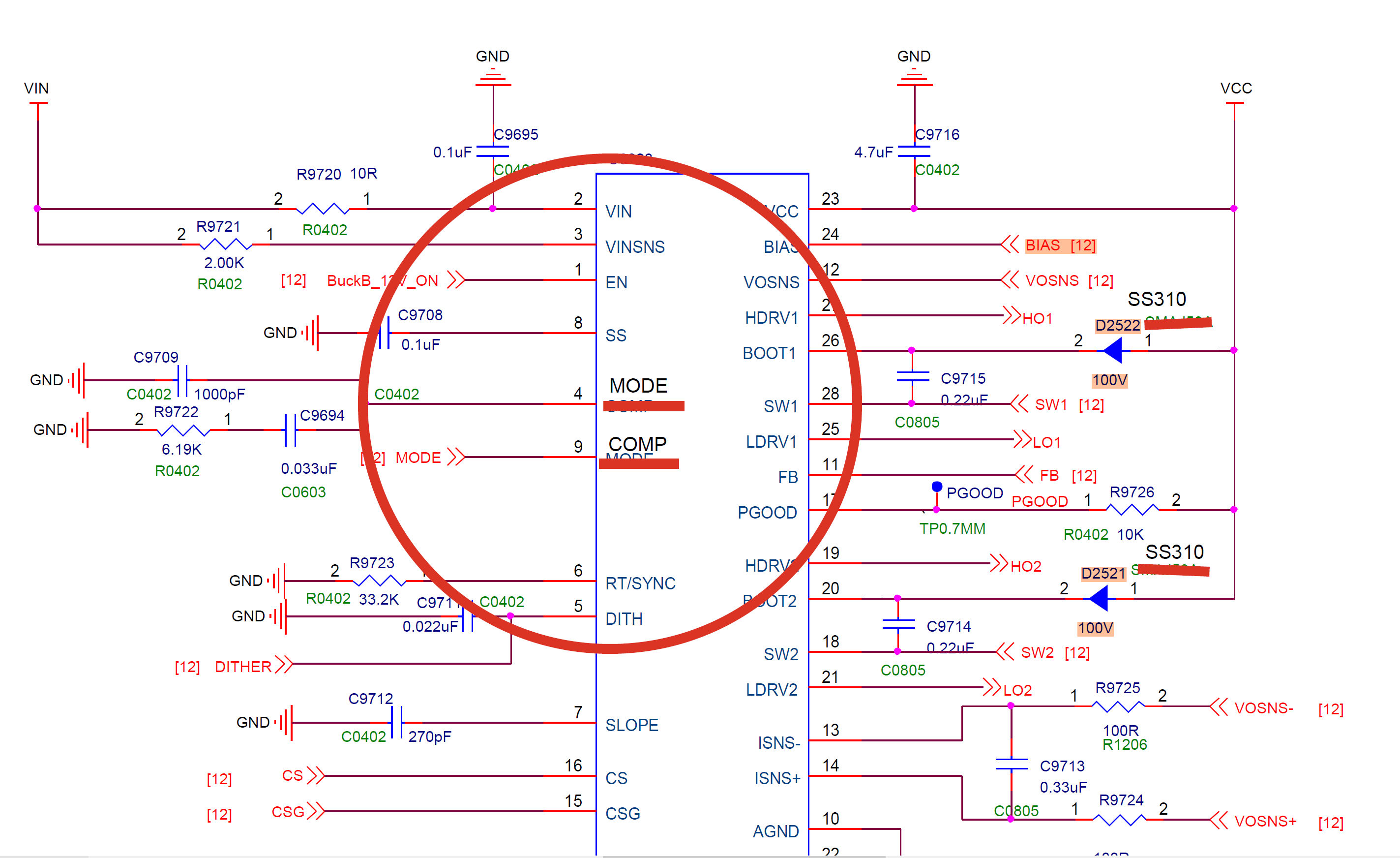

We are implementing an LM5176 for a router motherboard application.

The basic specifications are:

Vin = 8V-36

Vout = 12V

Imax = 6A

I have a first article board, and there is one other board that is currently in-use. Originally, we had startup issues and problems operating in Boost mode. We do not have a diode prior to the Vin pin, so I disabled Bias feedback by setting its input to ground. That cured the boot and low-V issues, and we seem to have good Vcc under all conditions.

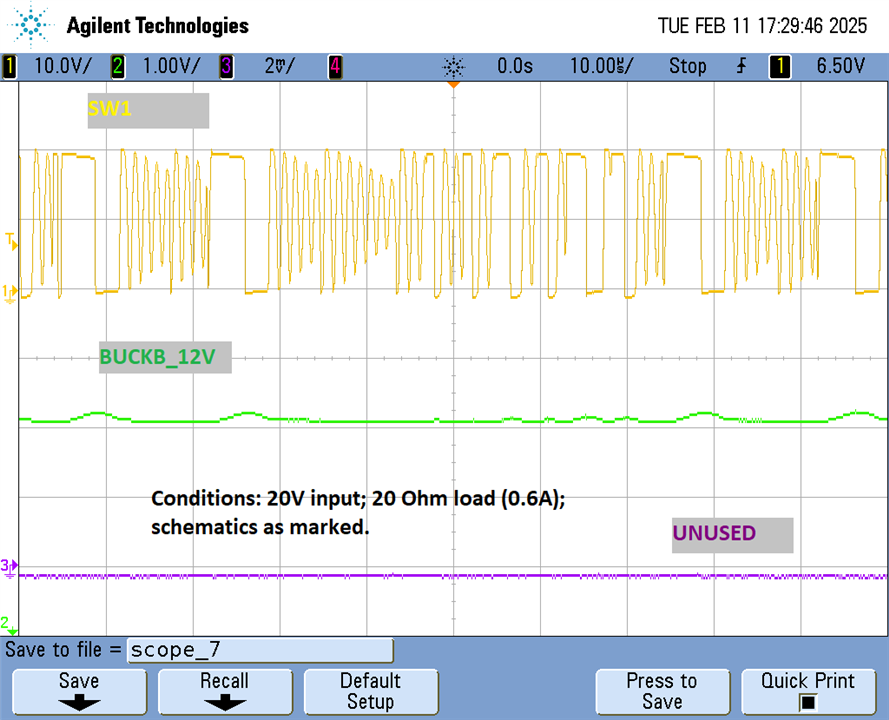

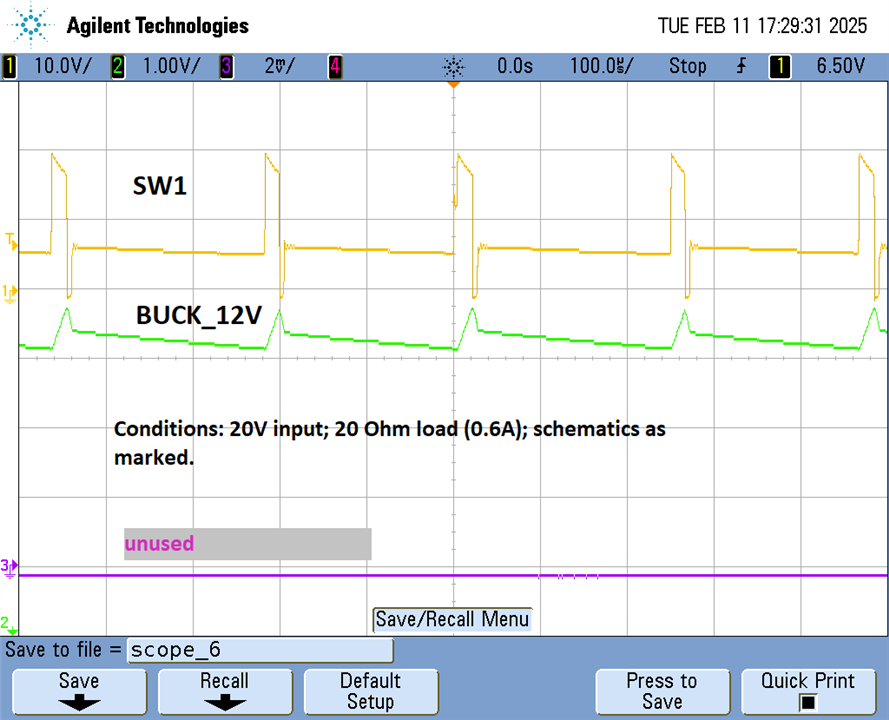

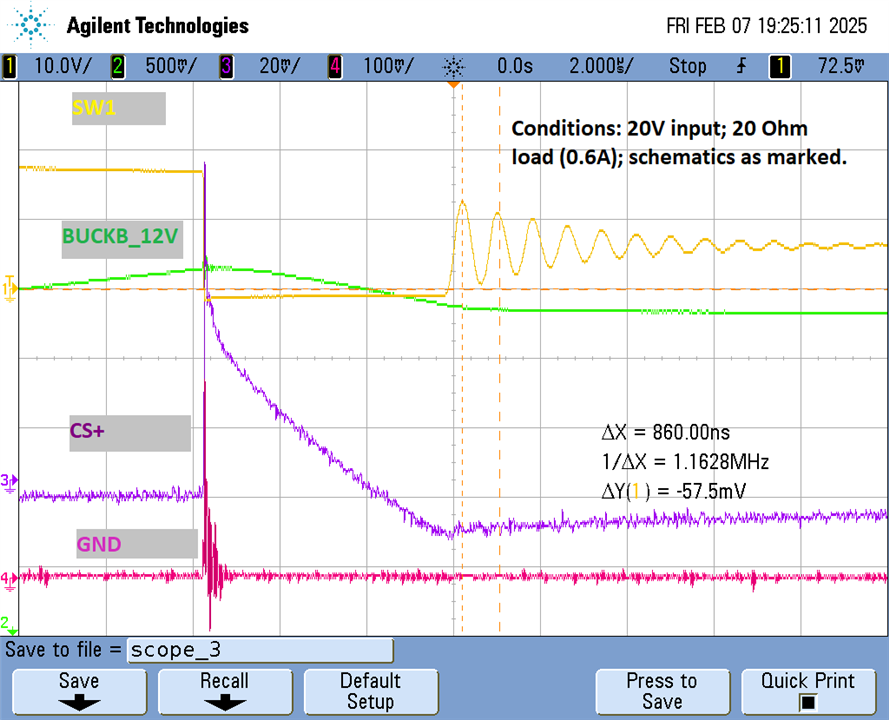

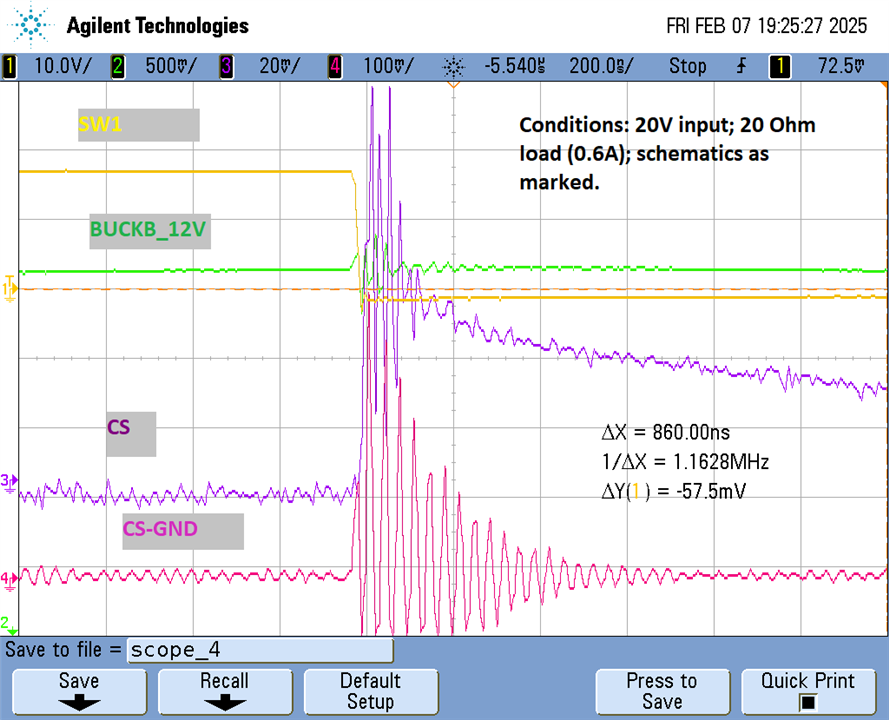

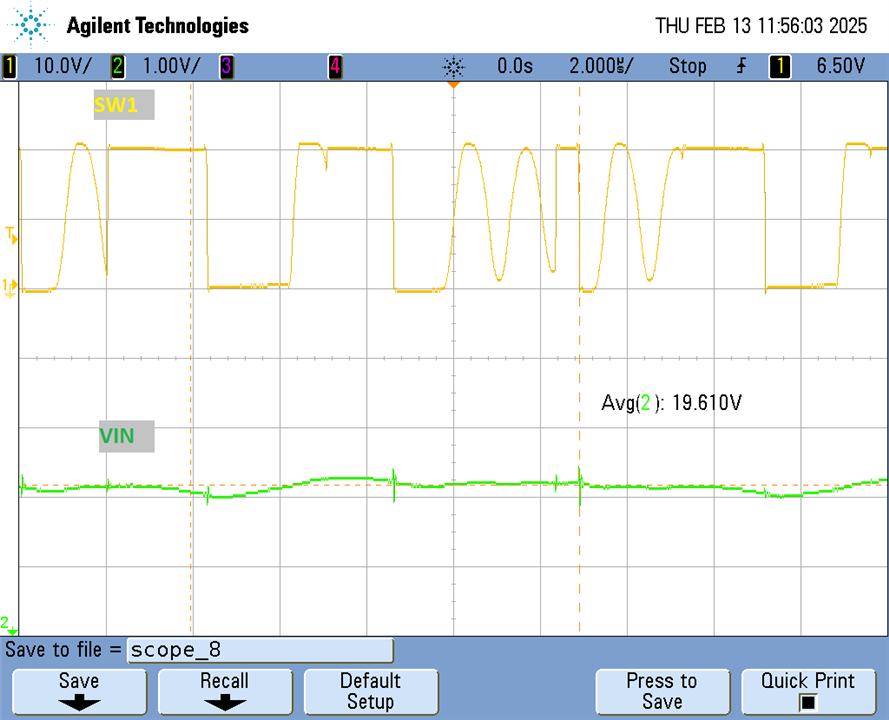

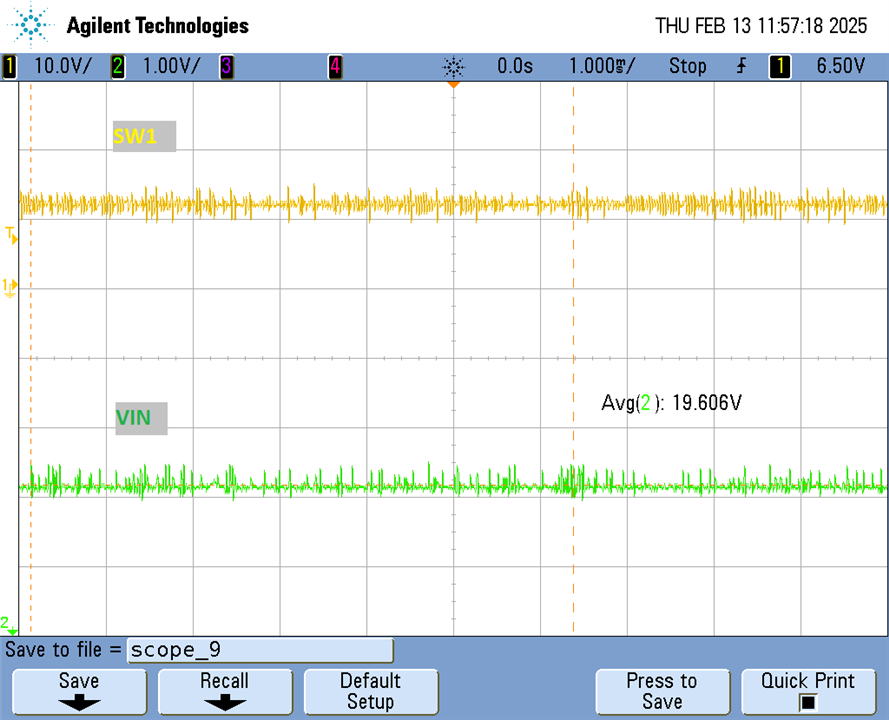

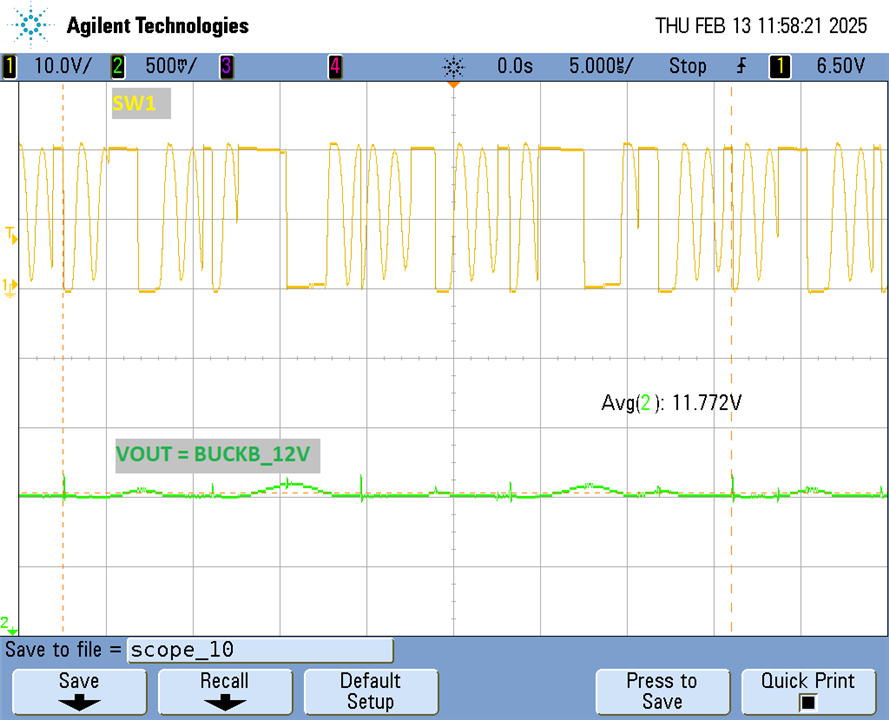

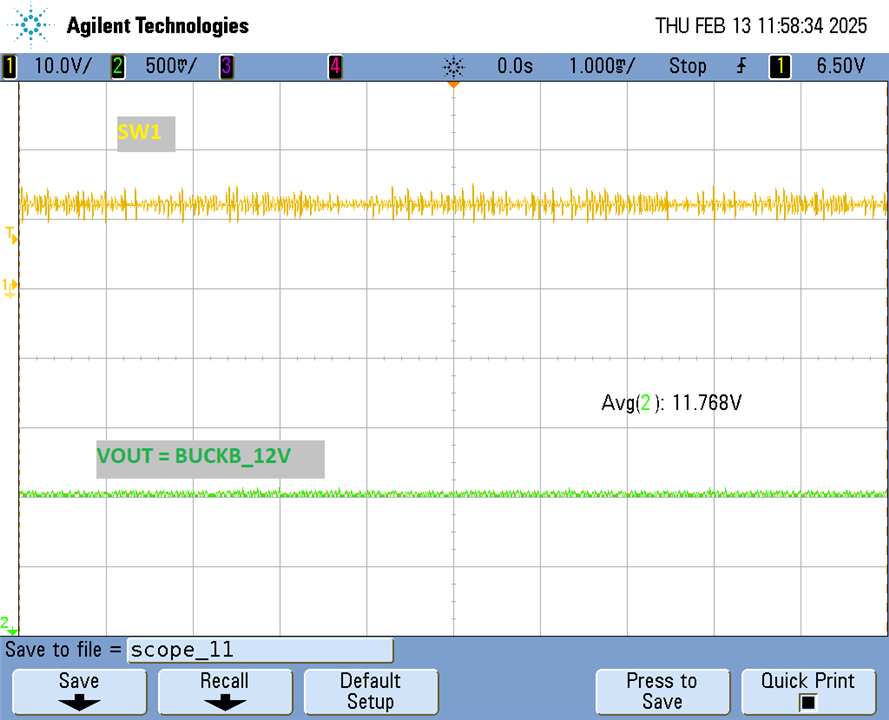

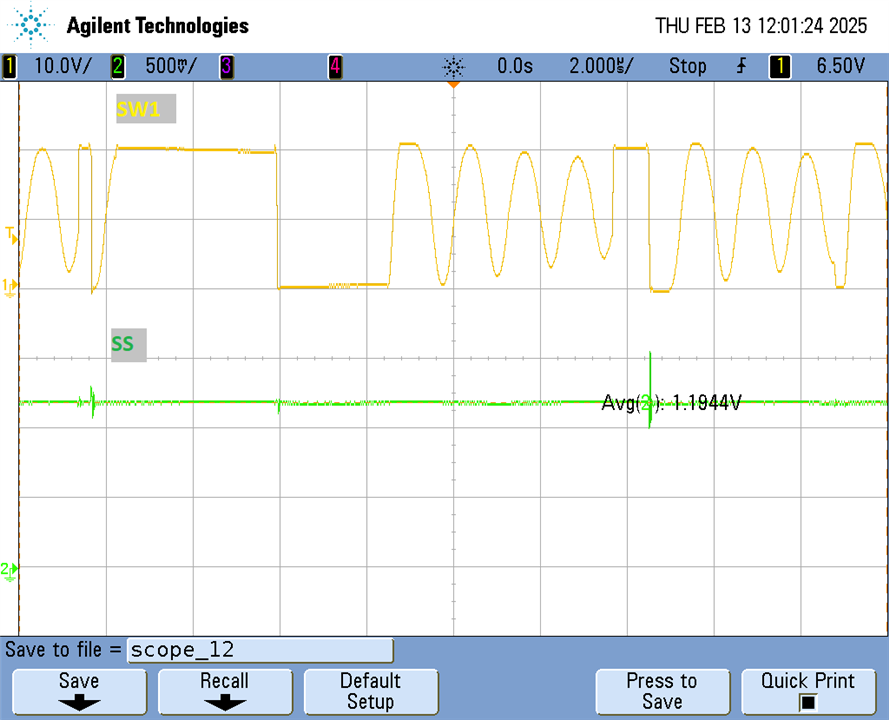

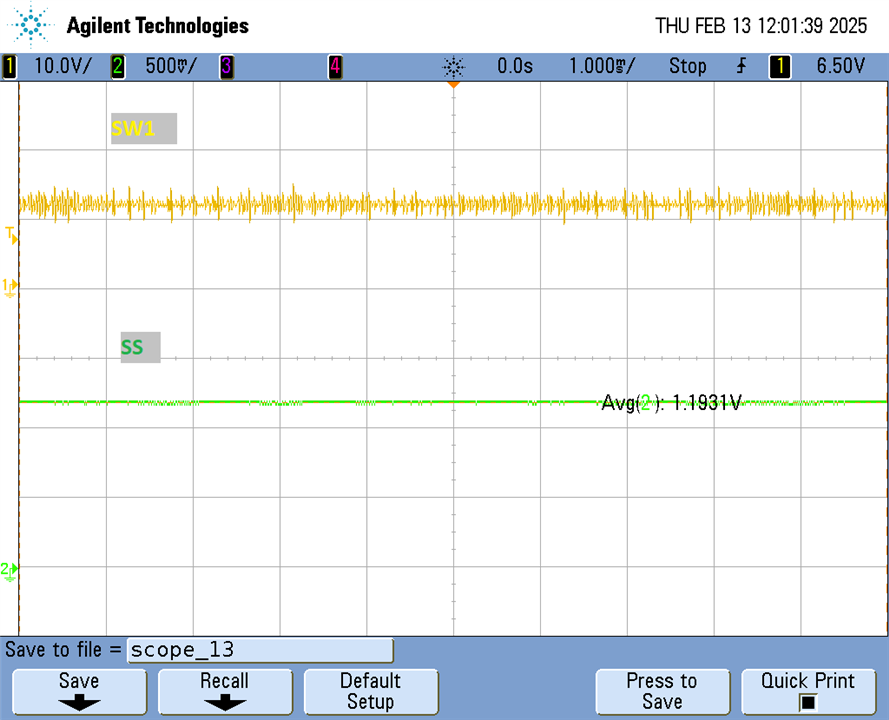

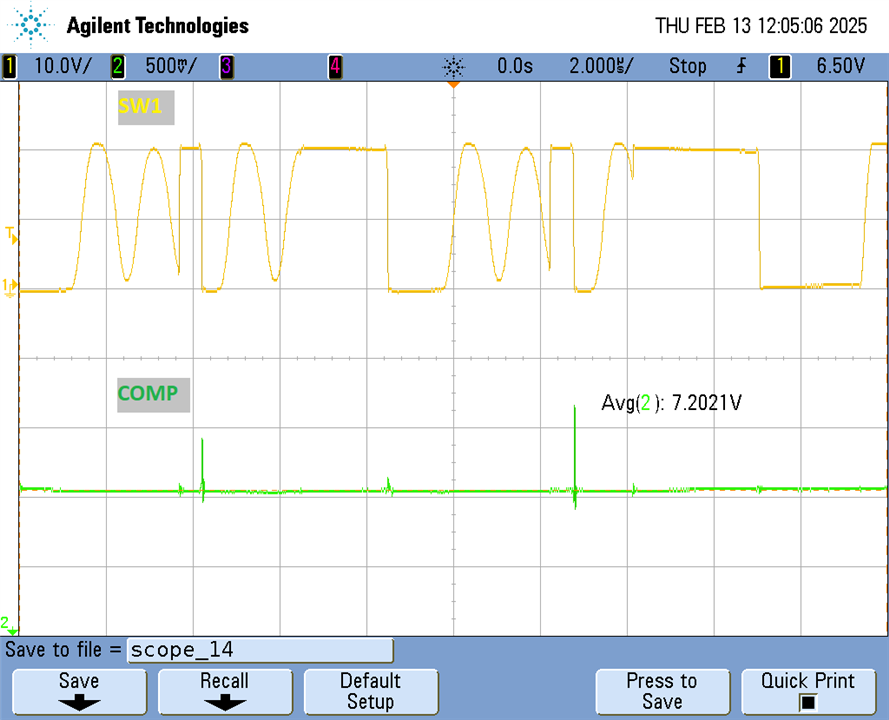

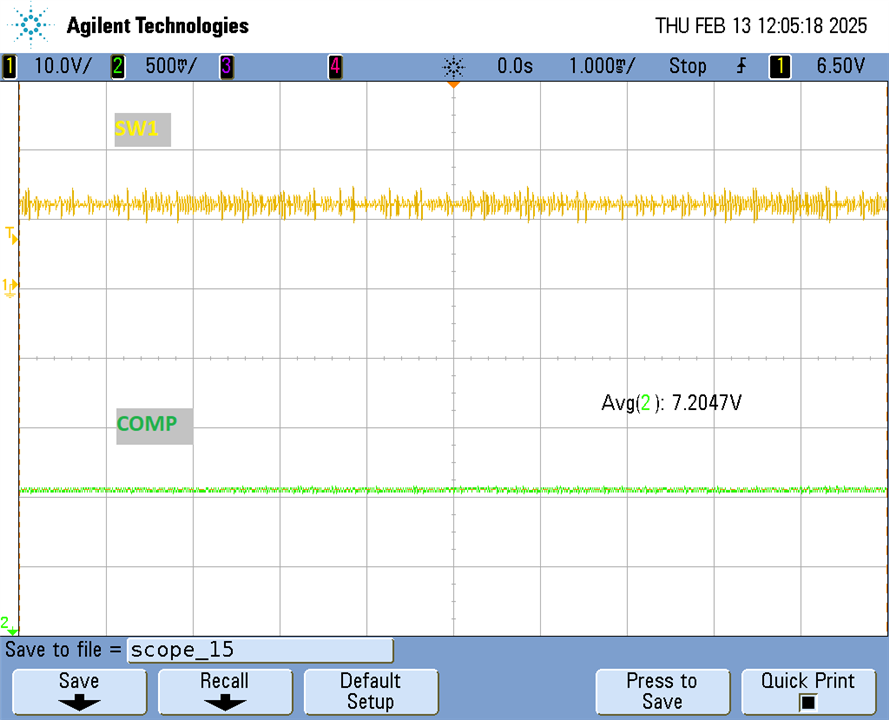

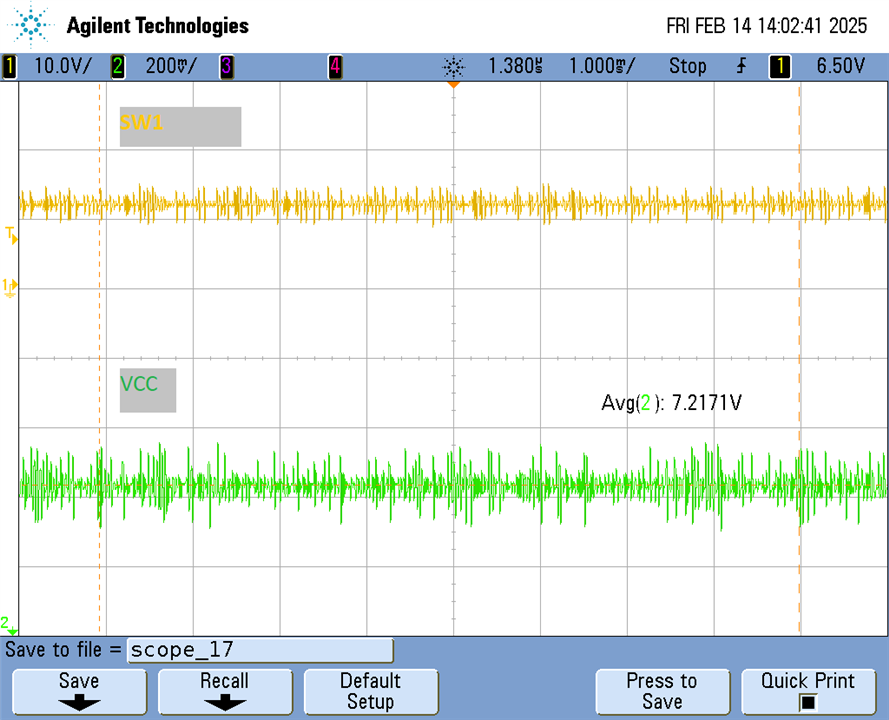

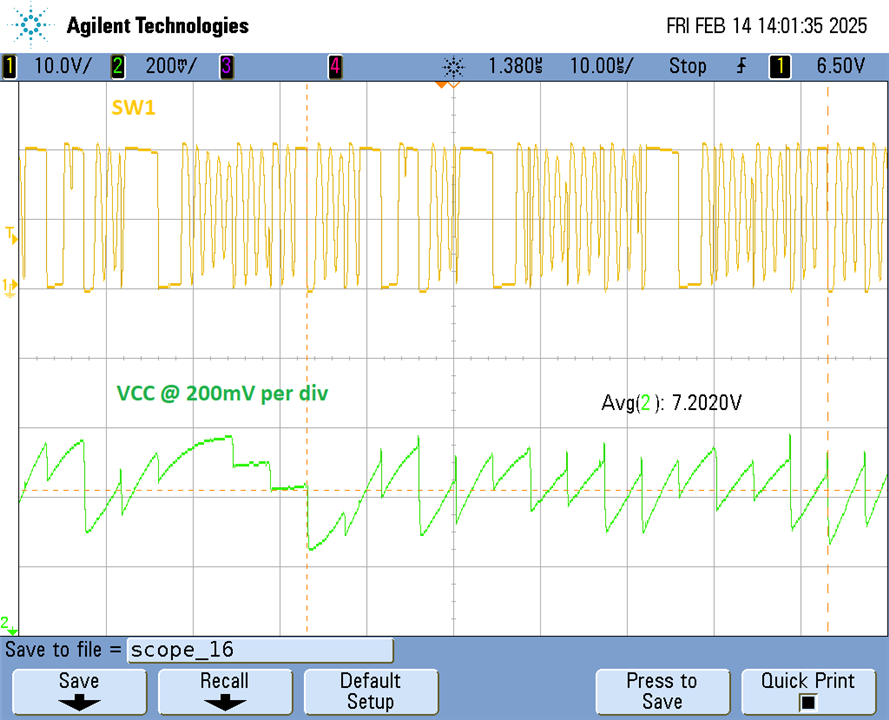

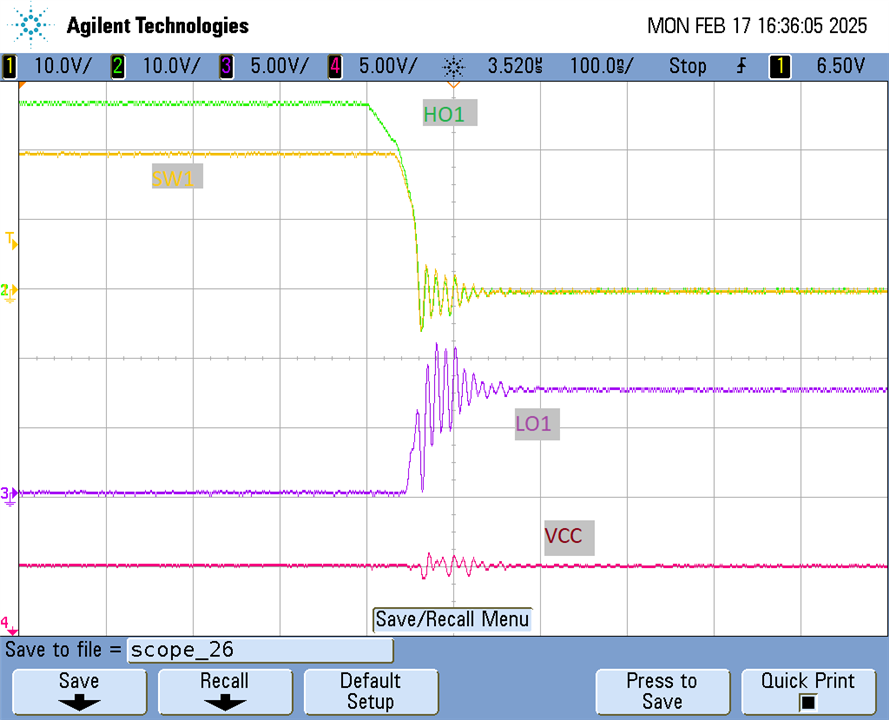

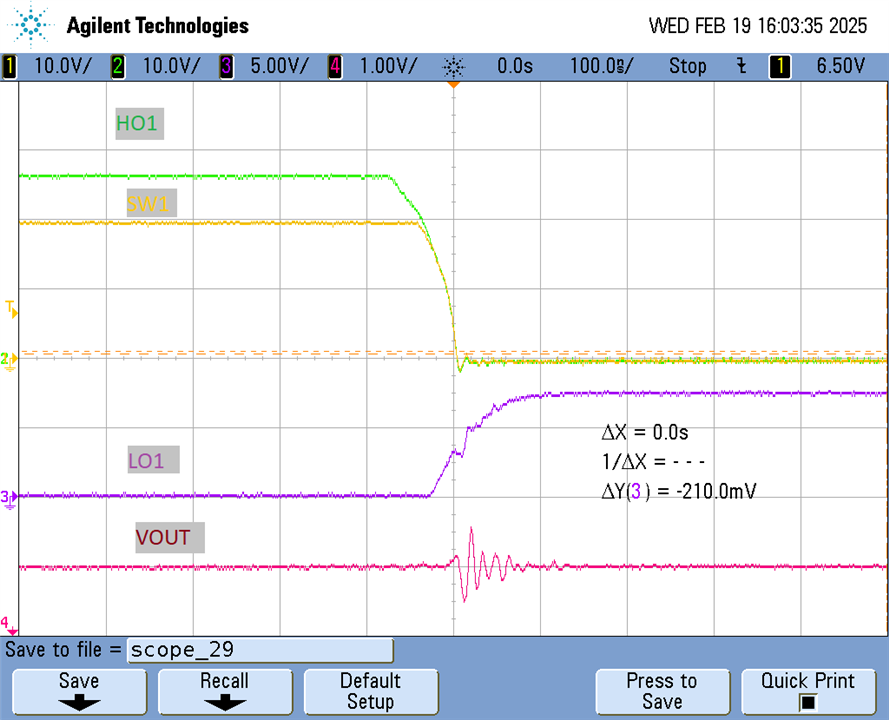

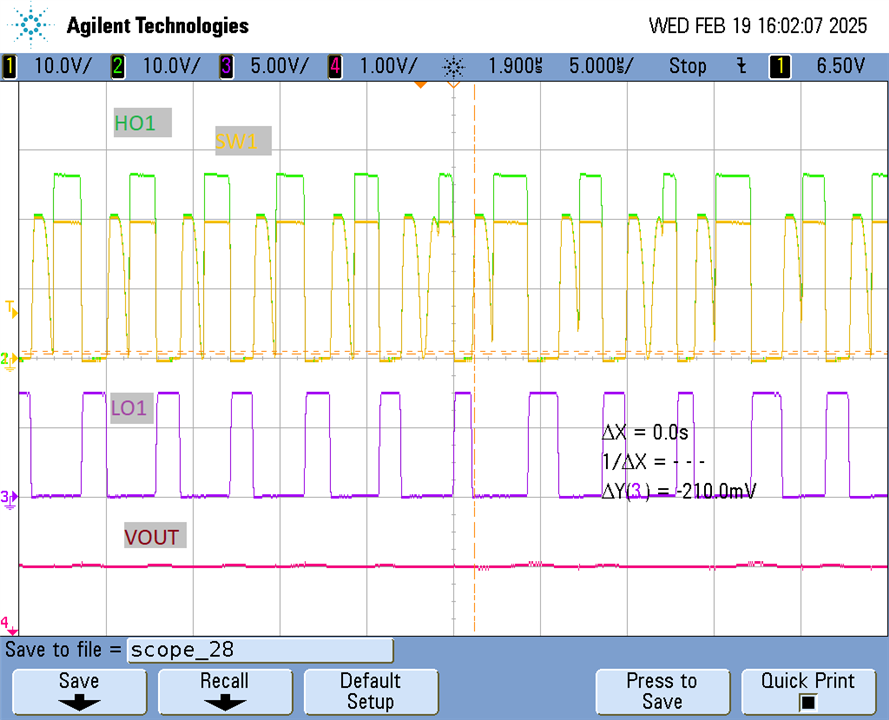

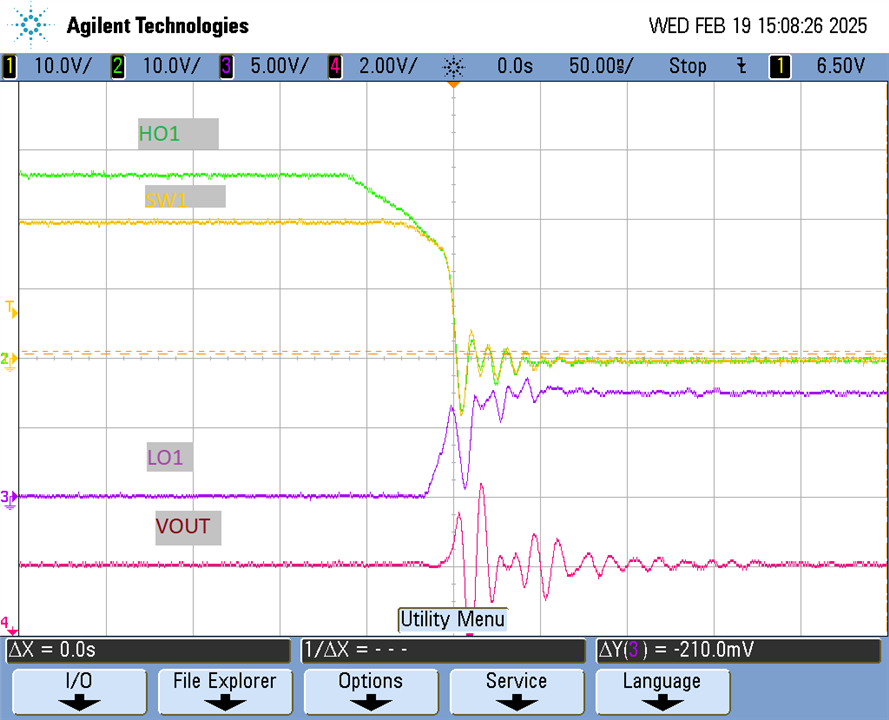

The issues are that the controller seems to be regularly cycle-skipping and (in one startup mode) ringing considerably between cycles. This seems to be a period where all switches are opened. We are not currently instrumented to observe the inductor current. We were able to use a Z0 probe (950 Ohms into a coax into a 50 Ohm terminator, 200x probe) which was soldered to the current sense resistor. The low-side current sense waveform looks ok, but one can observe significant ringing when the high-side switch turns off. (This could also be ground bounce.)