Other Parts Discussed in Thread: PMP22650, C2000WARE, SFRA,

Tool/software:

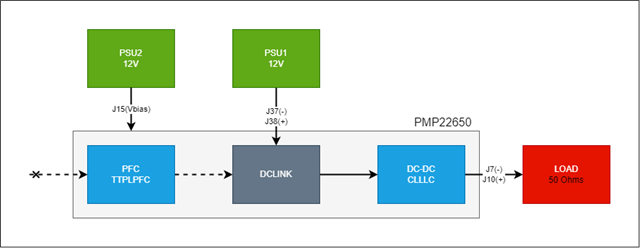

We're evaluating the PMP22650 reference design for a future project.

We've built a board and are testing the application based on the TMS320F28003x microcontroller. The base project we're using is from the tidm_02013 solution available in the C2000Ware DigitalPower SDK (5.04.00.00).

We've started with the CLLLC labs and we manage to complete the first one related to the PWM control of the controller board.

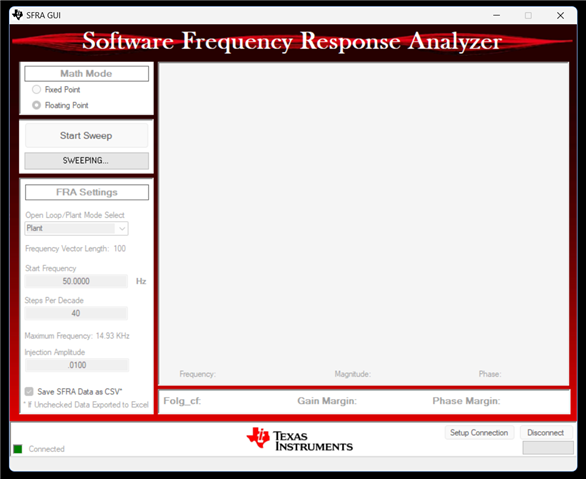

Now we're in Lab 2, where we need to use the SFRA application to characterise the plant and the open-loop parameters of the system.

Here we have a problem with the firmware. When we start the SFRA application, the frequency sweep never stops, so we think there must be something wrong with the board application, as we had to make some changes to get it to work.

- obc_7_4kw_user_settings.h:

- Update the defines to enable SFRA in CLLC.

- clllc_settings.h:

- Update the define CLLLC_SFRA_ALLOWED from the old board define `OBC_6_6KW_RUN_SFRA_ON_CLLLC` to the correct one `OBC_7_4KW_RUN_SFRA_ON_CLLLC`,

- Update the lab definition to lab 2.

```

...

#define CLLLC_LAB 2

- clllc_user_settings.h:

- Update the peripheral clock frequency from `50000000' to `30000000', which is required to transmit the SCI data at the correct baud rate.

```

- ttplpfc_settings.h:

- This shouldn't make any difference, but we've set the PFC lab to 1 as we're using a DC input on the primary side.

```

Process we followed to run the lab:

- Start the debug from ccs.

- When the application is stopped in main:

- activate the real time mode

- start the js script to activate the variables to monitor the clllc lab2

- Apply voltage to the primary (10V).

- Start the application.

- Disable the trim by writing 1 in the 'CLLLC_clearTrip' variable.

- At this point we can observe the control PWM switching at the desired frequency (500kHz).

- At this point we start the SFRA application and we can connect to the board (connected indicator turns green).

- The application starts the sweep and does not change its state (tested for 5 hours).

Thank you for your help.