Other Parts Discussed in Thread: TPS7H5001-SP, PSPICE-FOR-TI

Tool/software:

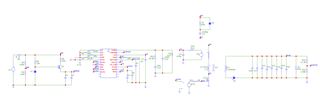

I'm having trouble simulating the TPS7H500x family in SPICE. Using the unencrypted model for the TPS7H5006, I ran into an issue with the SS pin not supplying current to charge the SS capacitor. I tried the unencrypted TPS7H5002 model and hit an error that appeared to be left over test code (line 712, starting with EDUMMY) and commented that line out. Then I ran into the same issue as the TPS7H5006 model.

Nodes EN_LOGIC and N16635995 are going high, which appears to indicate all the start up conditions are met. X_U3 appears to turn on the soft start charging current (source G_G1), but at the same time, X_S2 appears to short it to ground.

Am I missing something here? Has anyone had success with these models