Tool/software:

Hi,

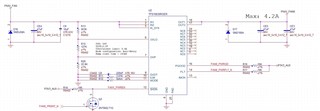

We use the TPS16630 for our new design for the cooling fan hot swappable protection, and we have below isseu for this design:

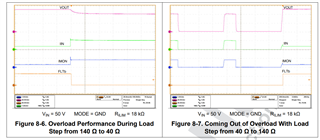

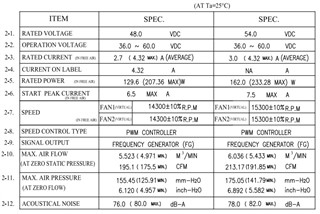

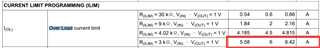

1. The max.starting current of pur fans is 7.5A, and TPS16630 over load current limit is 6A, and the holding time of the starting current of the fan is more than 3.2us,

so please advise if TPS16630 is the best choose for our desngi or not:

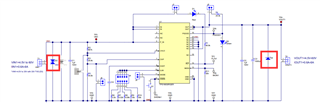

2. Please kindly review our schematic and advise if there is any error:

3. The below is the EVM reference, we want to remove the TVS because it is very large volume for our PCB, please advsie if this is available or not? thanks.