Tool/software:

Hello:

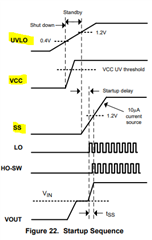

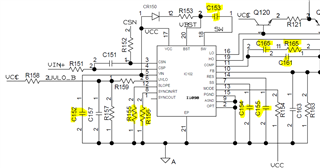

The following figure is the schematic diagram of the specific application peripheral circuit of the LM5122MHX/NOPB chip. The input voltage VIN+ is stepped down and stabilized by LDO to output VCC (10v) to power the chip. The input voltage VIN+ is connected to the chip CSP pin through the R151 (10kohm) resistor. The chip VCC (10V) is powered normally, and the UVLO pin voltage is divided by 1.5V (satisfying greater than 1.2V).

The current fault phenomenon is:

1. At room temperature, under different VIN+ rising slopes (VIN+ rises from 0V to 28V), the chip works normally and LO is driven. The following figure shows the test waveform of VIN+28V input at room temperature (the rising slope is 1V/ms, that is, VIN+ rises from 0V to 28V in 28ms). The green CH3 channel is the VIN+ rising waveform, and the yellow CH1 channel is the LO waveform.

2. At low temperature of -40℃, when the input VIN+ rising slope is 1V/ms (i.e. VIN+ rises from 0V to 28V in 28ms), the chip works abnormally and LO is not driven. The following figure shows the test waveform of low temperature of -40℃, input VIN+28V (rising slope is 1V/ms, i.e. VIN+ rises from 0V to 28V in 28ms). The green color of CH3 channel is the VIN+ rising waveform, and the yellow color of CH1 channel is the LO waveform.

Please help analyze the following problem: The chip does not work at low temperature, in a specific input slope range, and the explanation of the mechanism