Tool/software:

Dear Team,

Kindly review the below schematics and pcb layout and let me know your feedback.

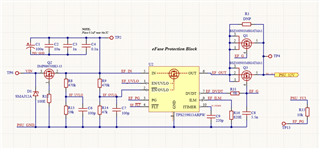

Schematics Snippet:

Question) Is there a requirement of Gate resistor when using multiple mosfets in parallel?

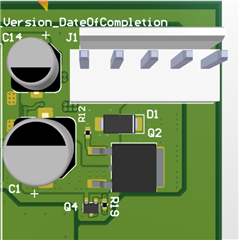

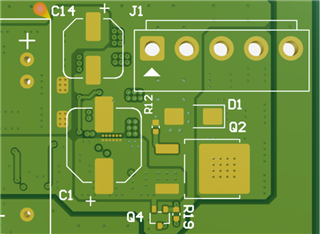

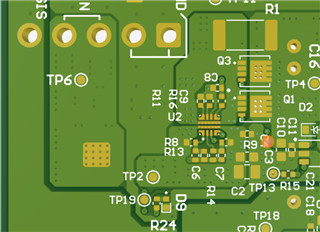

Layout Snippets: Top View

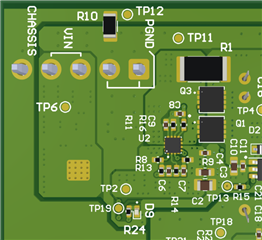

Bottom View

Designed on 4L Board with [L1(PWR+GND+SIG) / L2(GND) / L3(PWR+GND+SIG) / L4(PWR+GND+SIG)] Stackup

Power Characteristics: 12V @ 8A(max)

Kindly provide your feedback at the earliest.

Thanks and Regards,

Shashank

Electronics Engineer